www.ti.com

4.3SDRAMConfigurationRegister(SDCFG)

DDR2MemoryControllerRegisters

TheSDRAMconfigurationregister(SDCFG)containsfieldsthatprogramtheDDR2memorycontrollerto

meetthespecificationoftheDDR2memory.ThesefieldsconfiguretheDDR2memorycontrollertomatch

thedatabuswidth,CASlatency,numberofinternalbanks,andpagesizeoftheexternalDDR2memory.

Bits0-14oftheSDCFGregisterareonlywriteablewhentheTIMUNLOCKbitissetto0(unlocked).See

Section2.11.1formoreinformationoninitializingtheconfigurationregistersoftheDDR2memory

controller.TheSDCFGisshowninFigure22anddescribedinTable20.

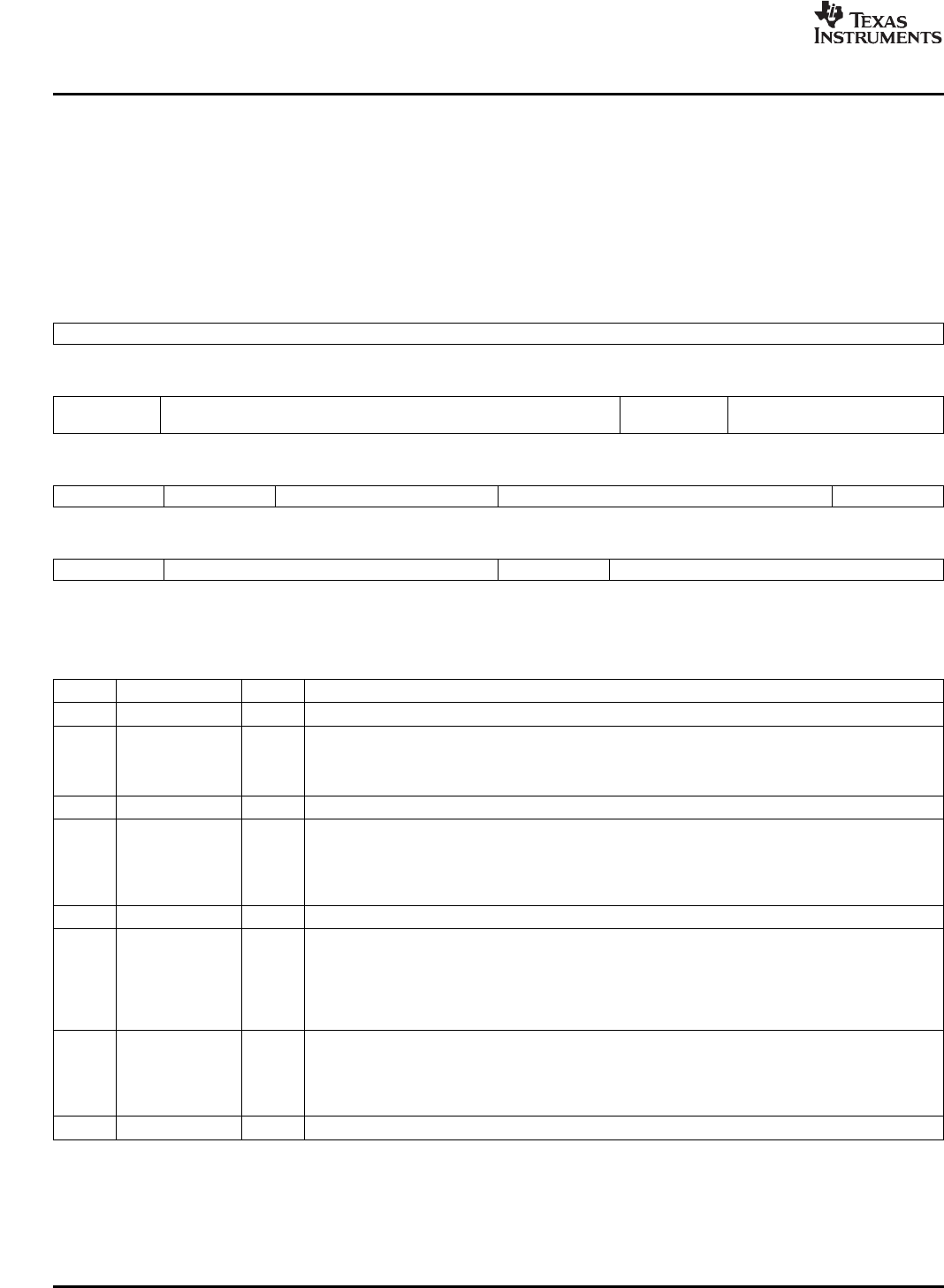

Figure22.SDRAMConfigurationRegister(SDCFG)

3124

Reserved

R-0x0

232219181716

BOOT_

ReservedDDR_DRIVEReserved

UNLOCK

R/W-0R/W-0xAR-0R-0x3

151413121198

TIMUNLOCKNMReservedCLReserved

R/W-0R/W-0R-0x0R/W-0x5R-0x0

764320

ReservedIBANKReservedPAGESIZE

R-0x0R/W-0x2R-0x0R/W-0x0

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table20.SDRAMConfigurationRegister(SDCFG)FieldDescriptions

BitFieldValueDescription

31-24ReservedReserved.Writestothisregistermustkeepthesebitsattheirdefaultvalues.

23BOOT_UNLOCKBootunlockbit.Controlswriteaccesstobits16through22ofthisregister.

0Writestobits22:16ofthisregisterarenotpermitted

1Writestobits22:16ofthisregisterareallowed

22-19ReservedReserved.Writestothisregistermustkeepthesebitsattheirdefaultvalue.

18DDR_DRIVEDDR2SDRAMdrivestrength.ThisbitisusedtoselectthedrivestrengthusedbytheDDR2

SDRAM.ThisbitiswriteableonlywhenBOOT_UNLOCKisunlocked(setto1).

0Normaldrivestrength

1Weak(60%)drivestrength

17-16ReservedReserved.Writestothisregistermustkeepthesebitsattheirdefaultvalue.

15TIMUNLOCKTimingunlockbit.ControlswriteaccessfortheSDRAMTimingRegister(SDTIM1)andSDRAM

TimingRegister2(SDTIM2).AwritetothisbitwillcausetheDDR2MemoryControllertostartthe

SDRAMinitializationsequence.

0RegisterfieldsintheSDTIM1andSDTIM2registersmaynotbechanged.

1RegisterfieldsintheSDTIM1andSDTIM2registersmaybechanged.

14NMDDR2databuswidth.AwritetothisbitwillcausetheDDR2MemoryControllertostarttheSDRAM

initializationsequence.

032-bitbuswidth.

116-bitbuswidth

13-12ReservedReserved.Thereservedbitlocationisalwaysreadas0.Avaluewrittentothisfieldhasnoeffect.

38DSPDDR2MemoryControllerSPRUEK5A–October2007

SubmitDocumentationFeedback