2 Troubleshooting Procedures 2.4 System Board Troubleshooting

2-24 [CONFIDENTIAL] Satellite Pro S300, TECRA A10/S10/P10 Maintenance Manual (960-684)

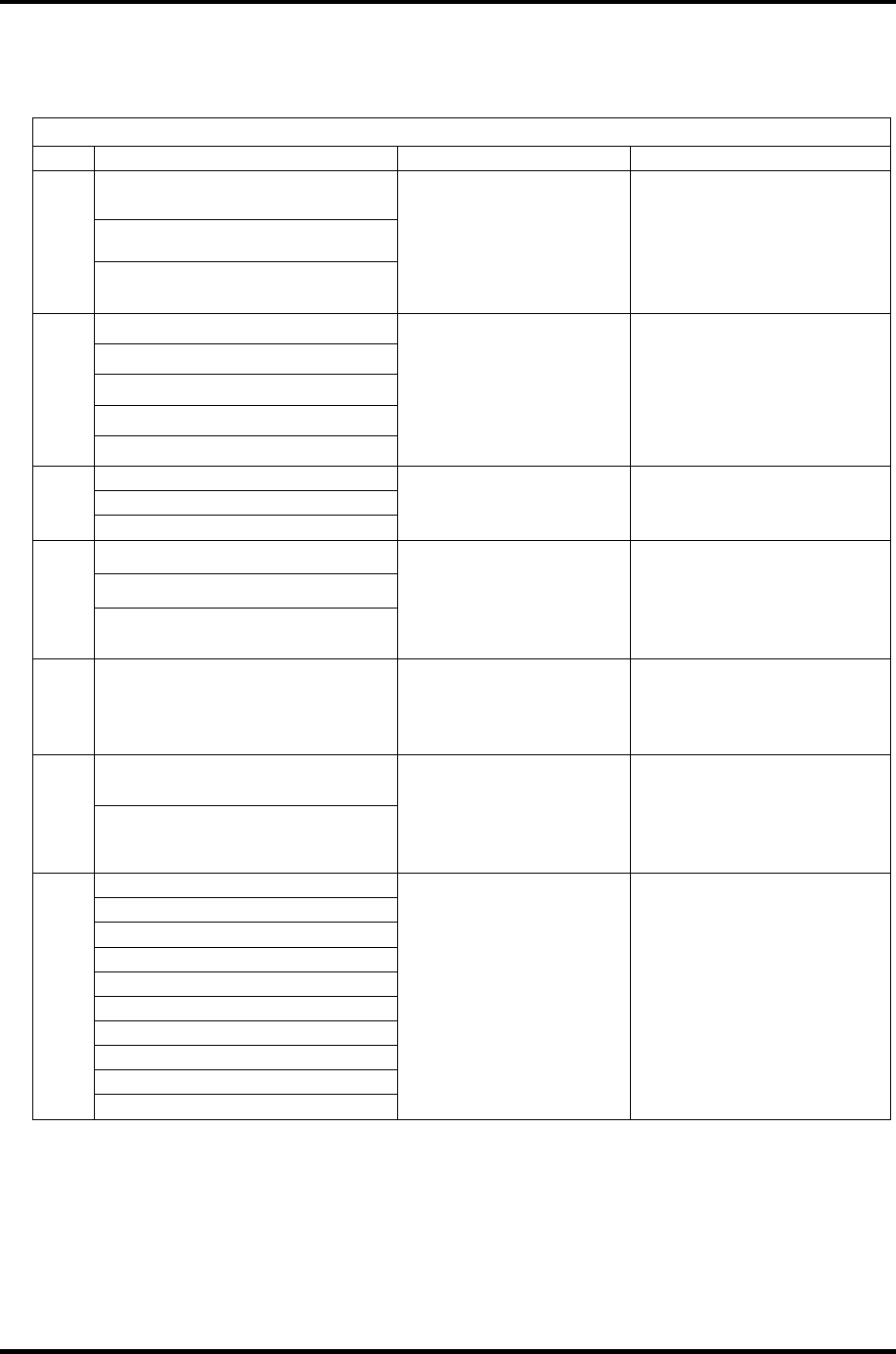

Table 2-5 Debug port error status (2/8)

System BIOS IRT processing

F100 CPU setup CPU IS1050 (CPU Socket)

Initialization of ICH, MCH, and

Super I/O

setup of SD controller

F101

setup of PIT

ICH(PCI register,

PIT controller)

MCH(PCI register )

card controller

BIOSROM

Super I/O

IS1050 (CPU Socket)

IC1200 (MCH)

IC1600 (ICH)

IC2000 (SD Cont.)

IC3000 (BIOS ROM)

IC3400 (Super I/O)

Memory initialization

Memory error

setup for using RAM area

check memory error of RAM area

F102

memory error

MCH(PCI register)

RAM(SPD, memory)

ICH(PCI register,

CMOS)

CPU

BIOSROM

IC1200 (MCH)

CN1400 (RAM Conn.)

CN1410 (RAM Conn.)

IC1600 (ICH)

IS1050 (CPU Socket)

IC3000 (BIOS ROM)

CPU setup

CMOS setup

F103

CMOS error

CPU

ICH(CMOS)

BIOSROM

IS1050 (CPU Socket)

IC1600 (ICH)

IC3000 (BIOS ROM)

Resume branch

BIOS processing reading

F104

ROM read error

ICH(CMOS)

BIOSROM

RAM

CN1400 (RAM Conn.)

CN1410 (RAM Conn.)

IC1600 (ICH)

IC3000 (BIOS ROM)

F105 check of BIOS processing

EC/KBC(EC), TPM,

CPU

IC3300 (TPM)

IC3200 (EC/KBC)

IC3200(EEPROM)

IS1050 (CPU Socket)

RAM setup

F106

Initialization of ICH (APIC)

CPU

ICH(CMOS,PIC

controller, I/O, MEM

I/O)

RAM

IS1050 (CPU Socket)

CN1400 (RAM Conn.)

CN1410 (RAM Conn.)

IC1600 (ICH)

Initialization of ICH (PIT)

PIT initialization error

CPU check

check of ROM data

SMI setup

Part number data distinction

Panel distinction

CMOS check

Clock generator setup

F107

CPU initialization

CPU

ICH(PIT controller,

MEM I/O, CMOS,I/O)

Clock generator,

EC/KBC(EC),

BIOSROM

Panel(EEPROM)

IC1000 (CLKGEN)

IS1050 (CPU Socket)

IC1600 (ICH)

IC3000 (BIOS ROM)

IC3200 (EC/KBC)

CN5000 (LCD Conn.)