Memory Maps and Registers

MVME2500 Installation and Use (6806800L01H)

96

5.5.16 PLD Watchdog Timer Refresh Register

The MVME2500 provides a watchdog timer refresh register.

CPU_RESET CPU_HRESET_REQ_L Reset Reason

1 - Reset is due to CPU_HRESET_REQ_L signal

0 -None

WD_TIMEOUT Watchdog Timeout Reset Reason

1 - Reset is due to watchdog timing out

0 - None

LRSTO TSI LRSTO Reset Reason

1 - Reset is due to LRSTO signal

0 - None

Sft_RST Soft Reset - Reset Reason

1 - Reset is due to Soft_RST register being set, or the front

panel switch being pressed more than three

0 - None

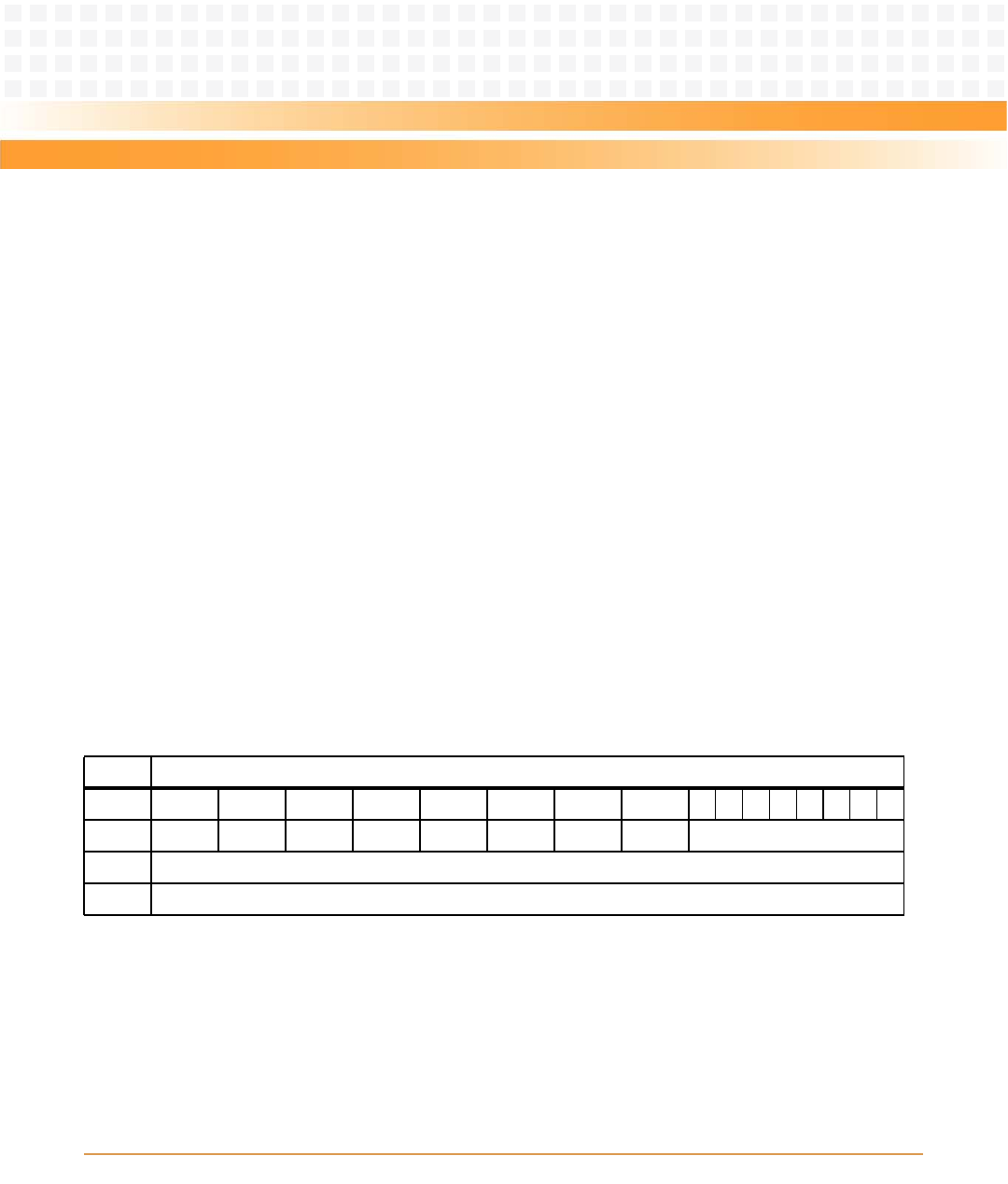

Table 5-19 PLD Watchdog Timer Refresh Register

REG PLD Watch Dog Timer Load - 0xFFC80600

Bit 15 14 13 12 11 10 9 8 76543210

Field RSVD RSVD RSVD RSVD RSVD RSVD RSVD RSVD Refresh

OPER R

RESET 0000

Field Description

Refresh Counter Refresh. When the pattern 0x00DB is written, the watchdog counter

will be reset to zero.