ICE CONTROL SOFTWARE ICS62XX

VIII-6 EPSON S1C62 FAMILY

DEVELOPMENT TOOL REFERENCE MANUAL

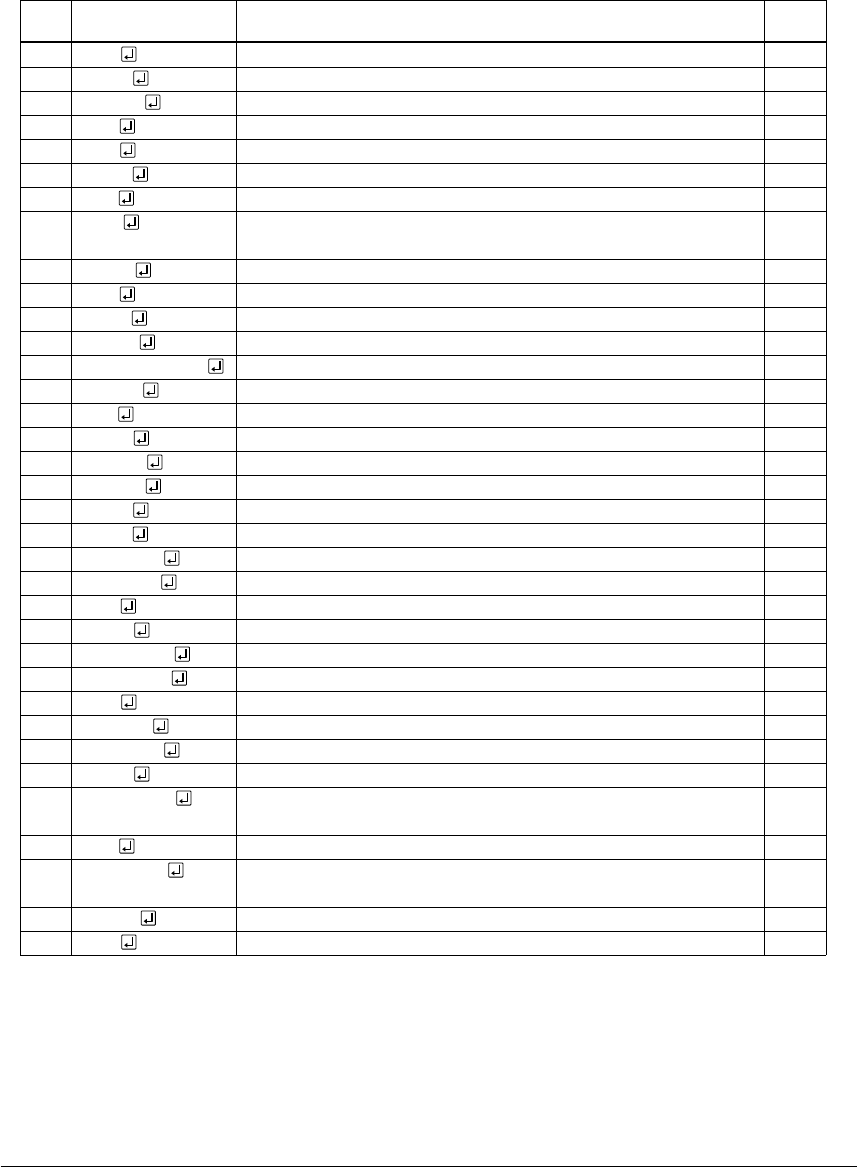

2.1.5 Alphabetical listing of commands

Tables 2.1.5.1(a) and (b) show an alphabetical listing of ICE commands.

Table 2.1.5.1(a) Alphabetical listing of commands

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

#A,a

#BA,a

#BAR,a

#BC

#BD

#BDR

#BE

#BM

#BMR

#BR

#BRR

#BRES

#BRKSEL,REM

#BSYN

#BT

#CHK

#CL,file

#CS,file

#CVD

#CVR

#DD,a1,a2

#DP,a1,a2

#DR

#DXY

#FD,a1,a2,d

#FP,a1,a2,d

#G,a

#H,p1,p2

#HA,a1,a2

#HAD

#HAR,a1,a2

#HB

#HC,S/C/E

#HELP

#HG

Assemble mnemonic instruction and store in address "a"

Set break at program address "a"

Cancel breakpoint

Display break condition

Set break condition for RAM data

Cancels the data RAM break condition

Break condition set for evaluation board CPU registers

Cancels the register break condition

All break conditions canceled

Sets BA clear/remain modes

Break disable mode

Sets break stop/trace mode

Reports results of ICE self diagnostic tests

Loads ICE set condition from file

Saves ICE set condition to file

Indicates coverage information

Clears coverage information

Displays contents of addresses a1 to a2 in the data area

Displays contents of addresses a1 to a2 in the program area

Displays evaluation board CPU internal registers

Displays X, Y and MX, MY

Sets d to addresses a1 to a2 in the data area

Sets d to addresses a1 to a2 in the program area

Executes the program from the "a" address

Displays history data for pointers 1 and 2

Sets up the history information acquisition from program area a1 to a2

Indicates the history acquisition program area

Sets up the prohibition of the history information acquisition

from program area a1 to a2

Displays upstream history data

Sets up the history information acquisition before

(S), before/after (C) and after (E) the break hit

Display ICE instructions

Display history data in 21 lines

VIII-38

VIII-52

VIII-52

VIII-58

VIII-53

VIII-53

VIII-66

VIII-56

Item

number

Command

configuration

Description of operation

Reference

page

Break enable mode

Assign multiple break condition for program address, RAM data

and registers

Cancels the multiple break condition

VIII-56

VIII-54

VIII-54

VIII-59

VIII-68

VIII-66

VIII-67

VIII-34

VIII-73

VIII-73

VIII-36

VIII-36

VIII-24

VIII-22

VIII-26

VIII-35

VIII-41

VIII-40

VIII-60

VIII-27

VIII-49

VIII-49

VIII-49

VIII-30

VIII-48

VIII-86

VIII-30