Hardware Overview 41

2.5.1.2 Set Associativity

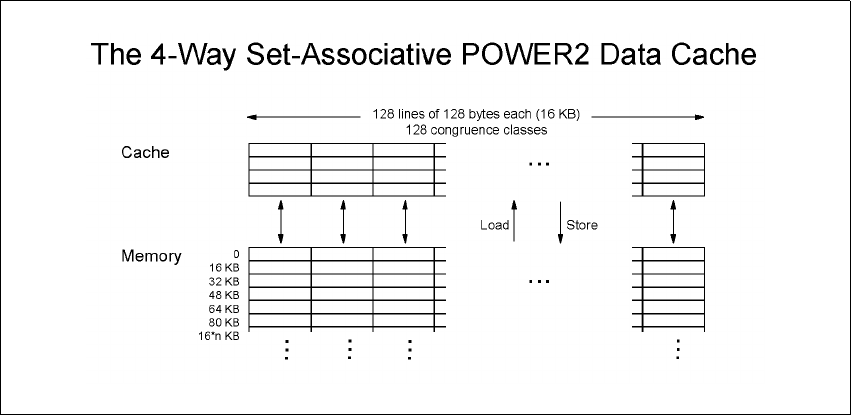

Set associativity is a mechanism that allows for more efficient sharing of the

L1 data cache among multiple programs running simultaneously. One of the

main differences between the POWER3 and the POWER2 (also PowerPC)

architectures is the way set associativity is implemented. PowerPC has a

4-way set-associative data cache, while POWER3 has a 128-way

set-associative data cache.

To gain a better understanding of set associativity, the concept of cache lines

needs to be introduced. A cache line is the basic unit of transfer between

main memory of cache. It is 128 bytes long on POWER3.

Conceptually, memory is sectioned into contiguous 128-byte lines, each one

starting on a cache-line boundary whose hardware address is a multiple of

128. The cache is similarly sectioned and all data transfer between cache and

memory is in units of these lines. If, for example, a particular floating point

number is required to be loaded into a floating point register, so that

computation may be done with it, then the whole cache line containing that

number is transferred from memory to cache.

Figure 13 shows the L1 data cache mapped onto memory, using POWER2,

while Figure 14 on page 42 shows it using POWER3.

Figure 13. The 4-Way Set Associative PowerPC/POWER2 L1 Data Cache