42 RS/6000 43P 7043 Models 150 and 260 Handbook

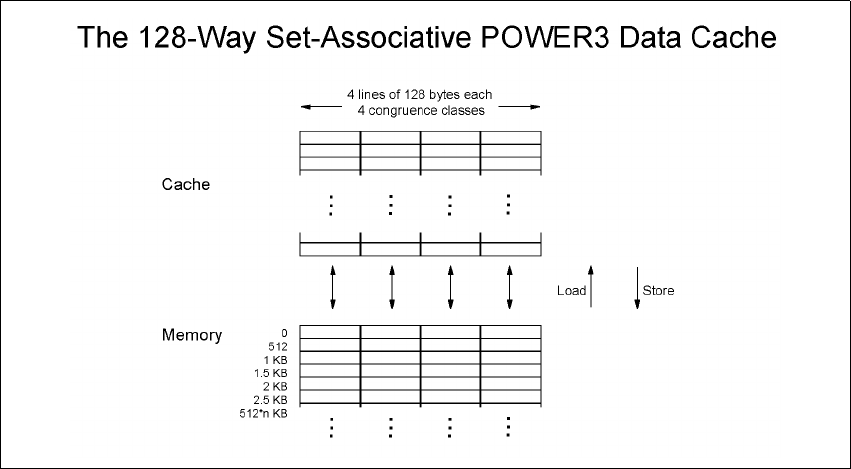

Figure 14. The 128-Way Set Associative POWER3 L1 Data Cache

Each cell represents a cache line; each column is called a congruence class.

Figure 13 on page 41 contains 128 congruence classes. There are four rows

in the cache area of the figure. Each of these rows contains 128 cache lines

of 128 bytes each (128 x 128 = 16 KB).

Any particular line from memory may only be loaded into a cache line in the

same congruence class: for POWER2, into one of only four locations; for

POWER3, into one of 128 locations.

Generally, when a new line from memory is loaded into the cache, existing

data must be displaced. If the previous contents of the line have been

modified, the line must be stored back into memory. The algorithm used by

the hardware for selecting which cache line to use is an approximation of

Least Recently Used on POWER2, and is Round-Robin on POWER3.

The set associative structure of the cache can lead to a reduction in its

effective size. Suppose successive data elements are being processed that

are regularly spaced in memory (that is with a constant stride). With the

POWER2 cache, the worst case is when the stride is exactly 16 KB (128 lines

X 128 bytes each) or a multiple of 16 KB. In this case, all elements will lie in

the same congruence class and the effective cache size will be only four