46 RS/6000 43P 7043 Models 150 and 260 Handbook

M (modified) The addressed sector is valid in this cache only. The value in

this sector has been changed in the cache, but the change is

not yet reflected in memory.

E (exclusive) The addressed sector is valid in this cache only. The data is

consistent with system memory.

S (shared) The addressed sector is valid in this cache and at least one

other cache. It is still consistent with system memory.

I (invalid) The addressed sector is not valid in the cache.

2.5.1.8 False Sharing

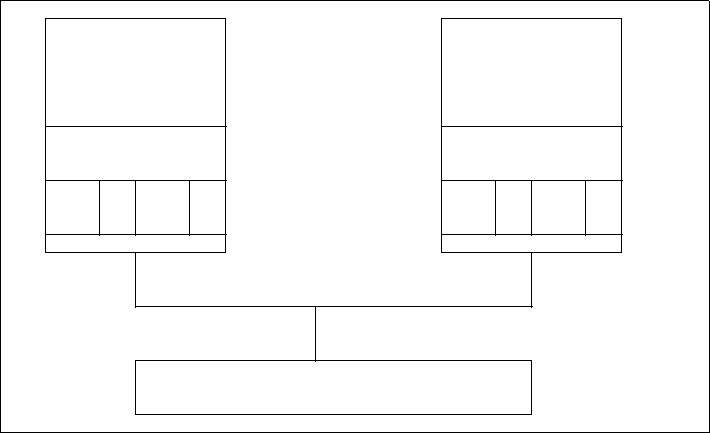

Figure 17 illustrates false sharing. Here, a whole cache unit of storage (a

cache sector in the case of the IBM SMP systems) is represented.

Figure 17. False Sharing

Suppose processor 1 and processor 2 loaded the same memory address in

their cache. If processor 1 changes only a portion of the cache sector, d1 for

example, the cache consistency logic will invalidate all the sectors in the

processor 2 cache. Then, if processor 2 tries to modify another portion of its

cache sector, d2, for example, which is still invalid since the whole sector is

invalid, a cache miss will occur. This is called false sharing.

Processor 1 Processor 2

Memory

Cache:

d1

d2...

Cache:

d1 d2...