Interfaces

44 Intel® Xeon® Processor E5-1600 v2/E5-2600 v2 Product Families

Datasheet Volume One of Two

2.5.2.6.9 DRAM Power Limit Data Write/Read

This feature allows the PECI host to program the power limit over a specified time or

control window for the entire DRAM domain covering all the DIMMs within all the

memory channels. Actual values are chosen based on DRAM power consumption

characteristics. The units for the DRAM Power Limit and Control Time Window are

determined as per the Package Power SKU Unit settings described in

Section 2.5.2.6.11. The DRAM Power Limit Enable bit in Figure 2-19 should be set to

activate this feature. Exact DRAM power limit values are largely determined by platform

memory configuration. As such, this feature is disabled by default and there are no

defaults associated with the DRAM power limit values. The PECI host may be used to

enable and initialize the power limit fields for the purposes of DRAM power budgeting.

Alternatively, this can also be accomplished through inband writes to the appropriate

registers. Both power limit enabling and initialization of power limit values can be done

in the same command cycle. All RAPL parameter values including the power limit value,

control time window, and enable bit will have to be specified correctly even if the intent

is to change just one parameter value when programming over PECI.

The following conversion formula should be used for encoding or programming the

‘Control Time Window’ in bits [23:17].

Control Time Window (in seconds) = ([1 + 0.25 * ‘x’] * 2

‘y’

) * ‘z’ where

‘x’ = integer value of bits[23:22]

‘y’ = integer value of bits[21:17]

‘z’ = Package Power SKU Time Unit[19:16] (see Section 2.5.2.6.13 for details on

Package Power SKU Unit)

For example, using this formula, a control time value of 0x0A will correspond to a

‘1-second’ time window. A valid range for the value of the ‘Control Time Window’ in

Figure 2-19 that can be programmed into bits [23:17] is 250 mS - 40 seconds.

From a DRAM power management standpoint, all post-boot DRAM power management

activities (also referred to as ‘DRAM RAPL’ or ‘DRAM Running Average Power Limit’)

should be managed exclusively through a single interface like PECI or alternatively an

inband mechanism. If PECI is being used to manage DRAM power budgeting activities,

BIOS should lock out all subsequent inband DRAM power limiting accesses by setting

bit 31 of the DRAM_POWER_LIMIT MSR or DRAM_PLANE_POWER_LIMIT CSR to ‘1’.

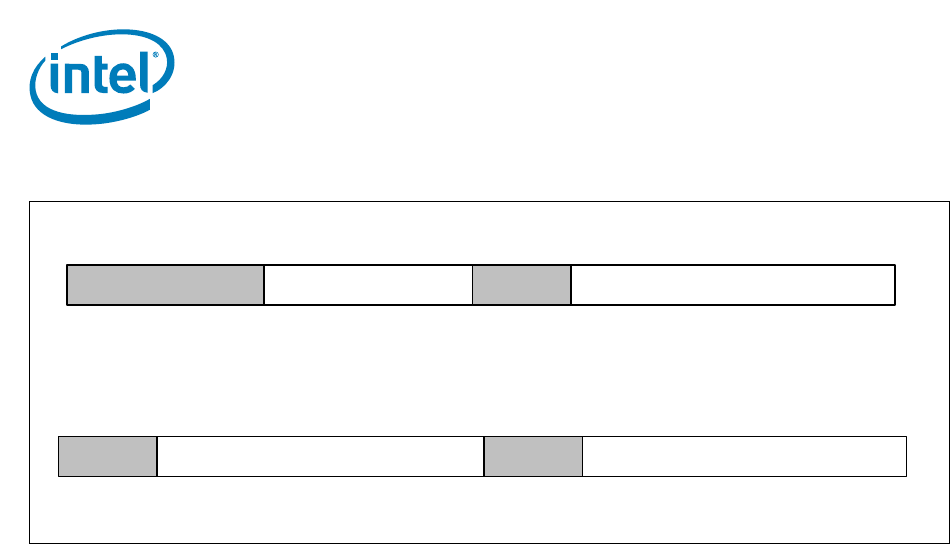

Figure 2-18. DRAM Power Info Read Data

DRAM_POWER_INFO (lower bits)

Reserved

14

Minimum DRAM Power

16

TDP DRAM Power

(Typical Value)

30 015

Reserved

31

DRAM_POWER_INFO (upper bits)

Maximum DRAM Power

3246

Reserved

47

Maximum Time

Window

4854

Reserved

5563