Interfaces

50 Intel® Xeon® Processor E5-1600 v2/E5-2600 v2 Product Families

Datasheet Volume One of Two

• CPU Microcode Update Revision: Reflects the revision number for the microcode

update and power control unit firmware updates on the processor sample. The

revision data is a unique 32-bit identifier that reflects a combination of specific

versions of the processor microcode and PCU control firmware.

• Machine Check Status: Returns error information as logged by the MCA Error

Source Log register. See Figure 2-26 for details. The power control unit will assert

the relevant bit when the error condition represented by the bit occurs. For

example, bit 29 will be set if the package asserted MCERR, bit 30 is set if the

package asserted IERR and bit 31 is set if the package asserted CAT_ERR_N. The

CAT_ERR_N may be used to signal the occurrence of a MCERR or IERR.

2.5.2.6.13 Package Power SKU Unit Read

This feature enables the PECI host to read the units of time, energy and power used in

the processor and DRAM power control registers for calculating power and timing

parameters. In Figure 2-27, the default value of the power unit field [3:0] is 0011b,

energy unit [12:8] is 10000b and the time unit [19:16] is 1010b. Actual unit values are

calculated as shown in Table 2-9.

Figure 2-25. Processor Microcode Revision

CPU microcode and PCU firmware revision

31

0

CPU code patch revision

Figure 2-26. Machine Check Status

MCA Error Source Log

Reserved

28

0

MCERRIERRCATERR

293031

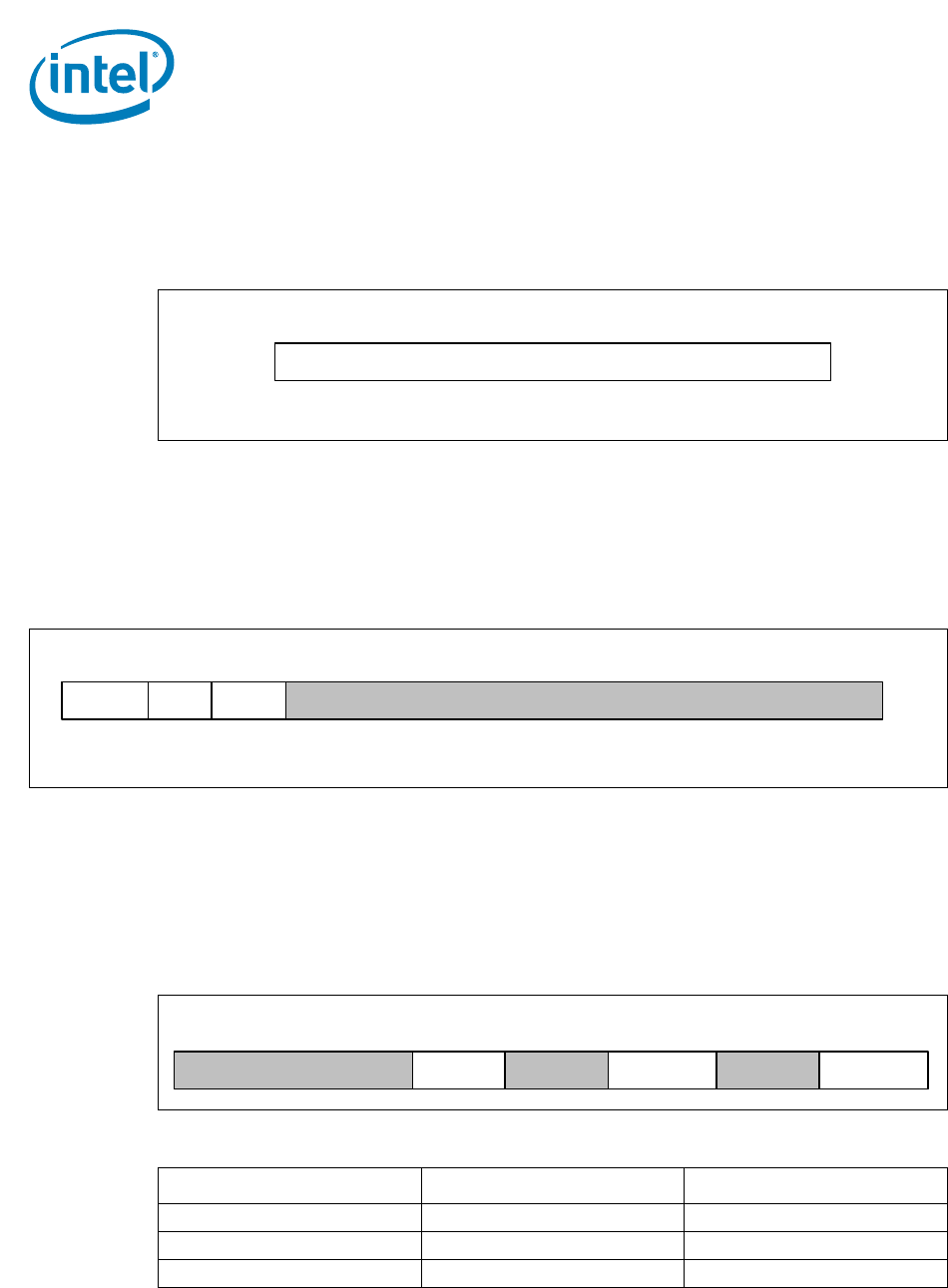

Figure 2-27. Package Power SKU Unit Data

Table 2-9. Power Control Register Unit Calculations

Unit Field Value Calculation Default Value

Time 1s / 2

TIME UNIT

1s / 2

10

= 976 µs

Energy 1J / 2

ENERGY UNIT

1J / 2

16

= 15.3 µJ

Power 1W / 2

POWER UNIT

1W / 2

3

= 1/8 W

Reserved

2031

Time Unit

19

Reserved

16 15

Energy Unit

12 8

Reserved Power Unit

13 7 4 3 0