Intel® Xeon® Processor E5-1600 v2/E5-2600 v2 Product Families 51

Datasheet Volume One of Two

Interfaces

2.5.2.6.14 Package Power SKU Read

This read allows the PECI host to access the minimum, Thermal Design Power and

maximum power settings for the processor package SKU. It also returns the maximum

time interval or window over which the power can be sustained. If the power limiting

entity specifies a power limit value outside of the range specified through these

settings, power regulation cannot be guaranteed. Since this data is 64 bits wide, PECI

facilitates access to this register by allowing two requests to read the lower 32 bits and

upper 32 bits separately as shown in Table 2-8. Power units for this read are

determined as per the Package Power SKU Unit settings described in

Section 2.5.2.6.13.

‘Package Power SKU data’ is programmed by the PCU firmware during boot time based

on SKU dependent power-on default values set during manufacturing. The TDP

package power specified through bits [14:0] in Figure 2-28 is the maximum value of

the ‘Power Limit1’ field in Section 2.5.2.6.26 while the maximum package power in bits

[46:32] is the maximum value of the ‘Power Limit2’ field.

The minimum package power in bits [30:16] is applicable to both the ‘Power Limit1’ &

‘Power Limit2’ fields and corresponds to a mode when all the cores are operational and

in their lowest frequency mode. Attempts to program the power limit below the

minimum power value may not be effective since BIOS/OS, and not the PCU, controls

disabling of cores and core activity.

The ‘maximum time window’ in bits [54:48] is representative of the maximum rate at

which the power control unit (PCU) can sample the package energy consumption and

reactively take the necessary measures to meet the imposed power limits.

Programming too large a time window runs the risk of the PCU not being able to

monitor and take timely action on package energy excursions. On the other hand,

programming too small a time window may not give the PCU enough time to sample

energy information and enforce the limit. The minimum value of the ‘time window’ can

be obtained by reading bits [21:15] of the PWR_LIMIT_MISC_INFO CSR using the PECI

RdPCIConfigLocal() command.

2.5.2.6.15 “Wake on PECI” Mode bit Write / Read

Setting the “Wake on PECI” mode bit enables successful completion of the

WrPCIConfigLocal(), RdPCIConfigLocal(), WrPCIConfig() and RdPCIConfig() PECI

commands by forcing a package ‘pop-up’ to the C2 state to service these commands if

the processor is in a low-power state. The exact power impact of such a ‘pop-up’ is

determined by the product SKU, the C-state from which the pop-up is initiated and the

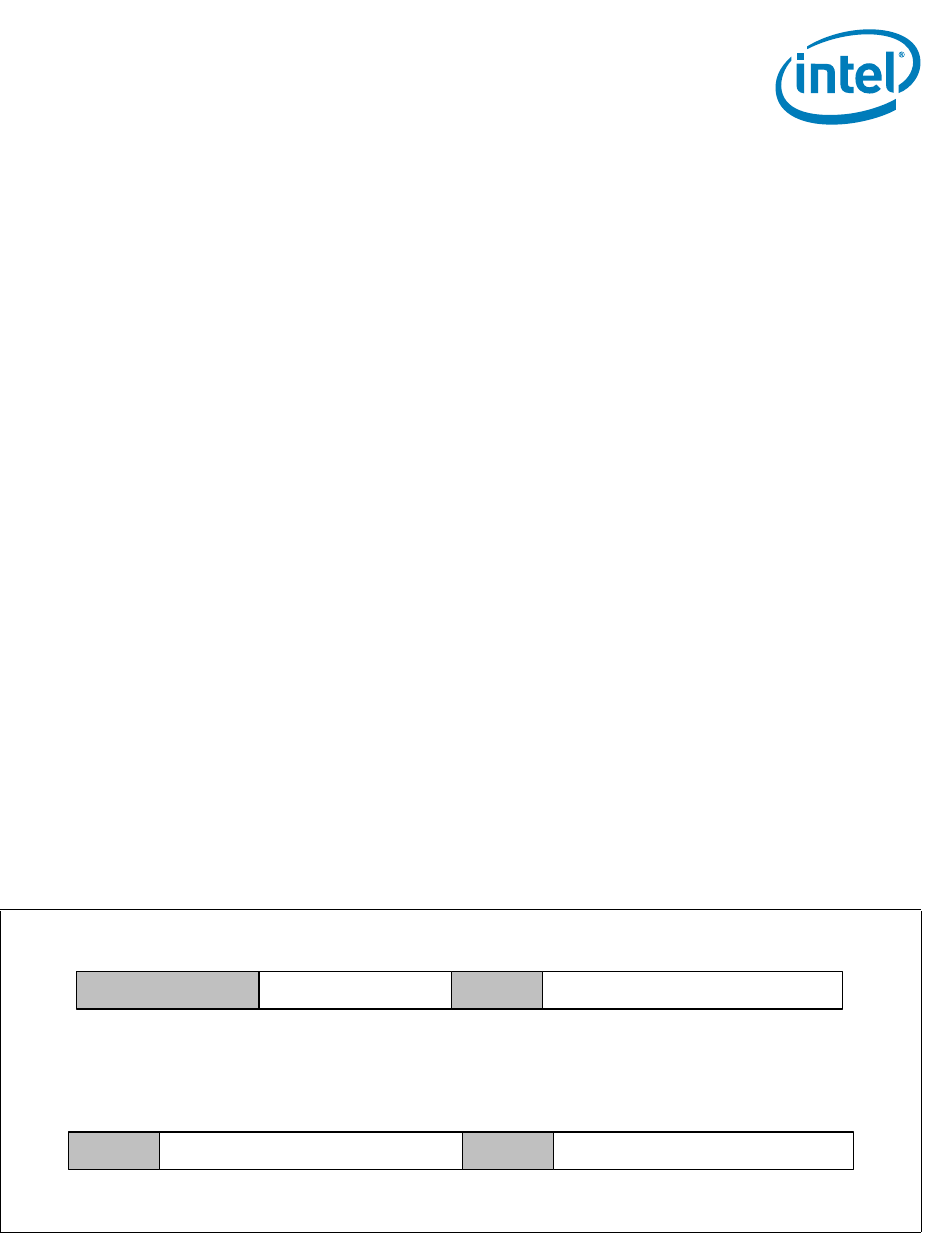

Figure 2-28. Package Power SKU Data

Package Power SKU (lower bits)

Reserved

14

Minimum Package Power

16

TDP Package Power

30 015

Reserved

31

Package Power SKU (upper bits)

Maximum Package Power

3246

Reserved

47

Maximum Time

Window

4854

Reserved

5563