Intel® Xeon® Processor E5-1600 v2/E5-2600 v2 Product Families 65

Datasheet Volume One of Two

Interfaces

completion code. Alternatively, reads to unimplemented or hidden registers may return

a completion code of 0x90 indicating an invalid request. It is also possible that reads to

function 0 of non-existent IIO devices issued prior to BIOS POST may return all ‘0’s

with a passing completion code. PECI originators can access this space even prior to

BIOS enumeration of the system buses. There is no read restriction on accesses to

locked registers.

PCI configuration addresses are constructed as shown in Figure 2-46. Under normal in-

band procedures, the Bus number would be used to direct a read or write to the proper

device. PECI reads to the processor IIO devices should specify a bus number of ‘0000’

and reads to the rest of the processor uncore should specify a bus number of ‘0001’ for

bits [23:20] in Figure 2-46. Any request made with a bad Bus number is ignored and

the client will respond with all ‘0’s and a ‘passing’ completion code.

2.5.2.9.1 Command Format

The RdPCIConfigLocal() format is as follows:

Write Length: 0x05

Read Length: 0x02 (byte), 0x03 (word), 0x05 (dword)

Command: 0xe1

Description: Returns the data maintained in the PCI configuration space within the

processor at the requested PCI configuration address. The Read Length dictates the

desired data return size. This command supports byte, word and dword responses as

well as a completion code. All command responses are prepended with a completion

code that includes additional pass/fail status information. Refer to Section 2.5.5.2 for

details regarding completion codes.

Note: The 3-byte PCI configuration address and read data field defined in Figure 2-47 are sent in standard PECI ordering with

LSB first and MSB last.

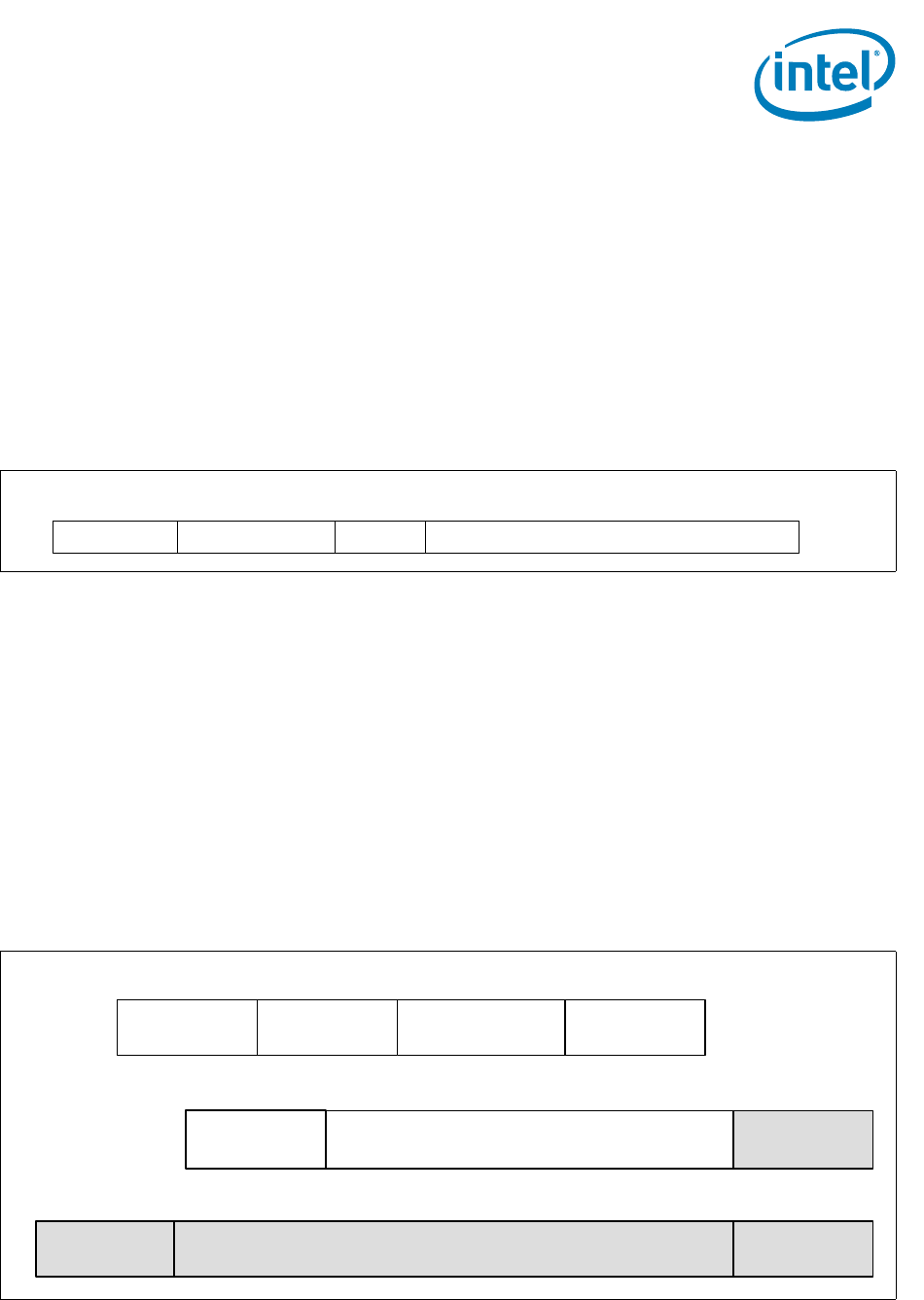

Figure 2-46. PCI Configuration Address for local accesses

20 19 15 1114 12 0

23

DeviceBus Function Register

Figure 2-47. RdPCIConfigLocal()

01 2 3

Byte #

FCS

12

7

9

Completion

Code

LSB PCI Configuration Address MSB

10

Write Length

0x05

LSB Data (1, 2 or 4 bytes) MSB

5

Cmd Code

0xe1

14

Read Length

{0x02,0x03,0x05}

68

Host ID[7:1] &

Retry[0]

Client Address

13

4

11

FCS

Byte

Definition