STL2 Server Board TPS STL2 Server Board Architecture Overview

Revision 1.0 2-11

The 82559 is a highly integrated PCI LAN controller for 10 or 100 Mbps Fast Ethernet

networks. As a PCI bus master, the 82559 can burst data at up to 132 MBps. This high-

performance bus master interface can eliminate the intermediate copy step in RX/TX frame

copies, resulting in faster frame processing.

The network OS communicates with the 82559 using a memory-mapped I/O interface, PCI

interrupt connected directly to the ICH, and two large receive and transmit FIFOs. The receive

and transmit FIFOs prevent data overruns or underruns while waiting for access to the PCI

bus, and also enable back-to-back frame transmission within the minimum 960ns inter-frame

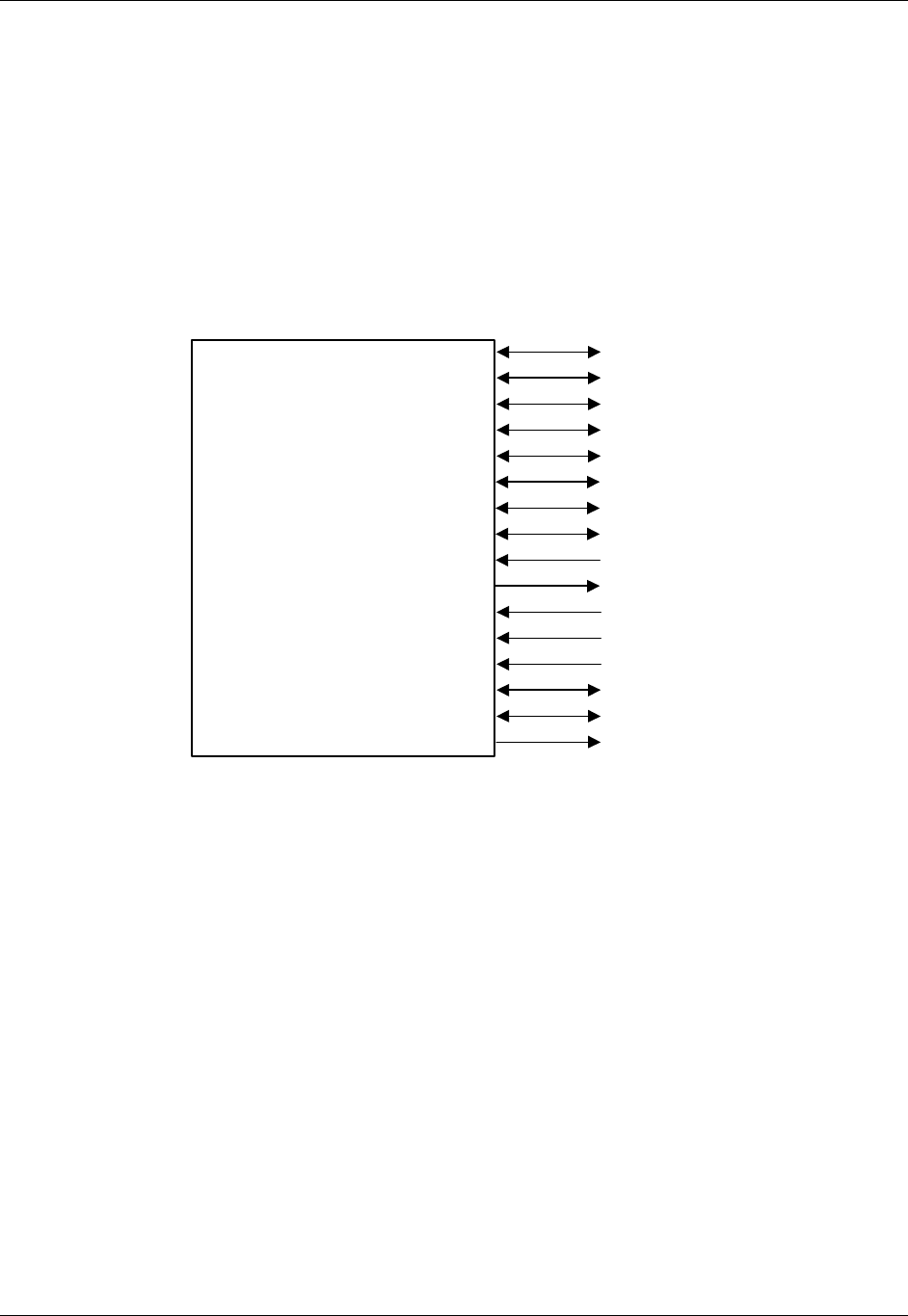

spacing. The figure below shows the PCI signals supported by the 82559:

i82559 NIC

PAR

STOP_L

TRDY_L

C/BE[3::0]_L

FRAME_L

AD[31::0]

SERR_L

PCI_CLK

RST_L

PERR_L

GNT_L

IRDY_L

DEVSEL_L

IDSEL

REQ_L

PCI_INT_L

Figure 2-1. Embedded NIC PCI Signals

2.4.2.1.1 Supported Network Features

The 82559 contains an IEEE MII compliant interface to the components necessary to

implement an IEEE 802.3 100Base TX network connection. The STL2 supports the following

features of the 82559 controller:

•

Glueless 32-bit PCI Bus Master Interface (Direct Drive of Bus), compatible with PCI Bus

Specification, revision 2.1 / 2.2.

•

Chained memory structure, with improved dynamic transmit chaining for enhanced

performance.

•

Programmable transmit threshold for improved bus utilization.

•

Early receive interrupt for concurrent processing of receive data.

•

On-chip counters for network management.

•

Autodetect and autoswitching for 10 or 100 Mbps network speeds.

•

Support for both 10 Mbps and 100 Mbps networks, full or half duplex-capable, with

back-to-back transmit at 100 Mbps.