8050

8050

D N/B Maintenance

D N/B Maintenance

75

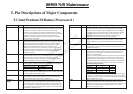

Host Interface Signal Descriptions

Signal Name Type Description

ADS#

I/O

AGTL+

Address Strobe: The system bus owner asserts ADS# to indicate the

first of two cycles of a request phase. The GMCH can assert this

signal for snoop cycles and

interrupt messages.

BNR#

I/O

AGTL+

Block Next Request: Used to block the current request bus owner

from issuing a new request. This signal is used to dynamically control

the CPU bus pipeline depth.

BPRI#

O

AGTL+

Bus Priority Request: The GMCH is the only Priority Agent on the

system bus. It asserts this signal to obtain the ownership of the

address bus. This signal has priority over symmetric bus requests and

will cause the current symmetric owner to

stop issuing new transactions unless the HLOCK# signal was

asserted.

BREQ0#

I/O

AGTL+

Bus Request 0#:

The GMCH pulls the processor bus BREQ

0#

signal

low during CPURST#. The signal is sampled by the processor on the

active-to-inactive transition of CPURST#. The minimum setup time

for this signal is 4 BCLKs. The minimum hold time is 2 clocks and

the maximum hold time is 20 BCLKs. BREQ0# should be tristated

after the hold time requirement has been satisfied.

During regular operation, the GMCH will use BREQ0# as an early

indication for FSB Address and Ctl input buffer and sense amp

activation.

CPURST#

O

AGTL+

CPU Reset: The CPURST# pin is an output from the GMCH. The

GMCH asserts CPURST# while RESET# (PCIRST# from ICH4-M)

is asserted and for approximately 1 ms after RESET# is deasserted.

The CPURST# allows the processor to begin execution in a known

state.

Note that the ICH4-M must provide CPU strap set-up and hold-times

around CPURST#.

This requires strict synchronization between GMCH, CPURST#

deassertion and ICH4-M driving the straps.

DBSY#

I/O

AGTL+

Data Bus Busy: Used by the data bus owner to hold the data bus for

transfers requiring more than one cycle.

DEFER#

O

AGTL+

Defer:

GMCH will generate a deferred response as defined by the

rules of the GMCH’s Dynamic Defer policy. The GMCH will also

use the DEFER# signal to indicate a CPU retry response.

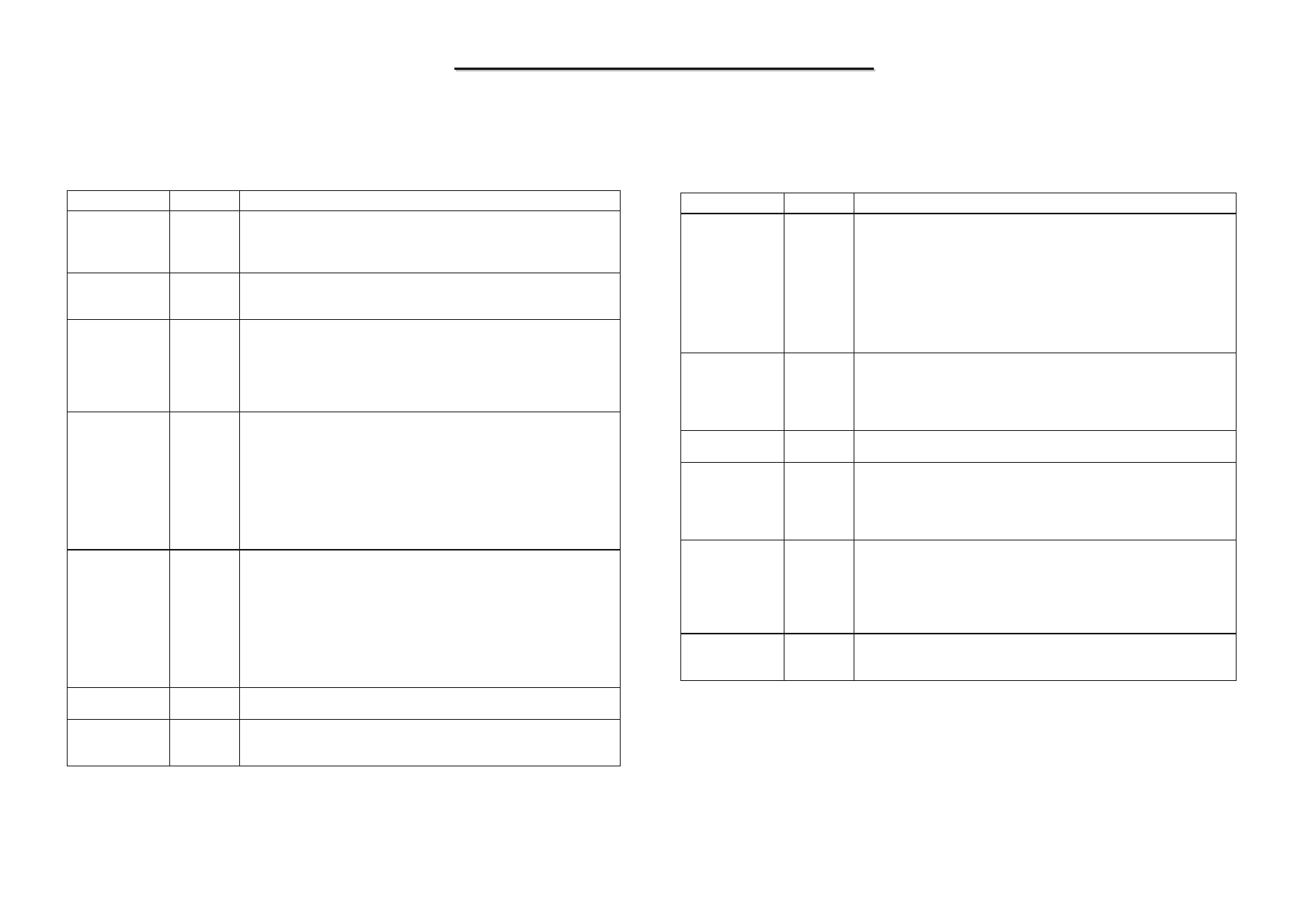

Signal Name Type Description

DINV[3:0]#

I/O

AGTL+

Dynamic Bus Inversion: Driven along with the HD[63:0]# signals.

Indicates if the associated signals are inverted or not. DINV[3:0]# are

asserted such that the number of data bits driven electrically low (low

voltage) within the corresponding 16-bit group never exceeds 8.

DINV# Data Bits

DINV[3]# HD[63:48]#

DINV[2]# HD[47:32]#

DINV[1]# HD[31:16]#

DINV[0]# HD[16:0]#

DPSLP#

I

CMOS

Deep Sleep #: This signal comes from the ICH4-M device, providing

an indication of C3 and C4 state control to the CPU. Deassertion of

this signal is used as an early indication for C3 and C4 wake up (to

active HPLL). Note that this is a low-voltage

CMOS buffer operating on the FSB VTT power plane.

DRDY#

I/O

AGTL+

Data Ready: Asserted for each cycle that data is transferred.

HA[31:3]#

I/O

AGTL+

Host Address Bus: HA[31:3]# connects to the CPU address bus.

During processor cycles the HA[31:3]# are inputs. The GMCH drives

HA[31:3]# during snoop cycles on behalf of Hub interface.

HA[31:3]# are transferred at 2x rate. Note that the

address is inverted on the CPU bus.

HADSTB[1:0]#

I/O

AGTL+

Host Address Strobe: HA[31:3]# connects to the CPU address bus.

During CPU cycles, the source synchronous strobes are used to

transfer HA[31:3]# and HREQ[4:0]# at the 2x transfer rate.

Strobe Address Bits

HADSTB[0]# HA[16:3]#, HREQ[4:0]#

HADSTB[1]# HA[31:17]#

HD[63:0]#

I/O

AGTL+

Host Data: These signals are connected to the CPU data bus.

HD[63:0]# are transferred at 4x rate. Note that the data signals are

inverted on the CPU bus.

5.2 Intel 855GM/GME North Bridge(1)

Host Interface Signal Descriptions(Continued)

MiTac Secret

Confidential Document