8050

8050

D N/B Maintenance

D N/B Maintenance

82

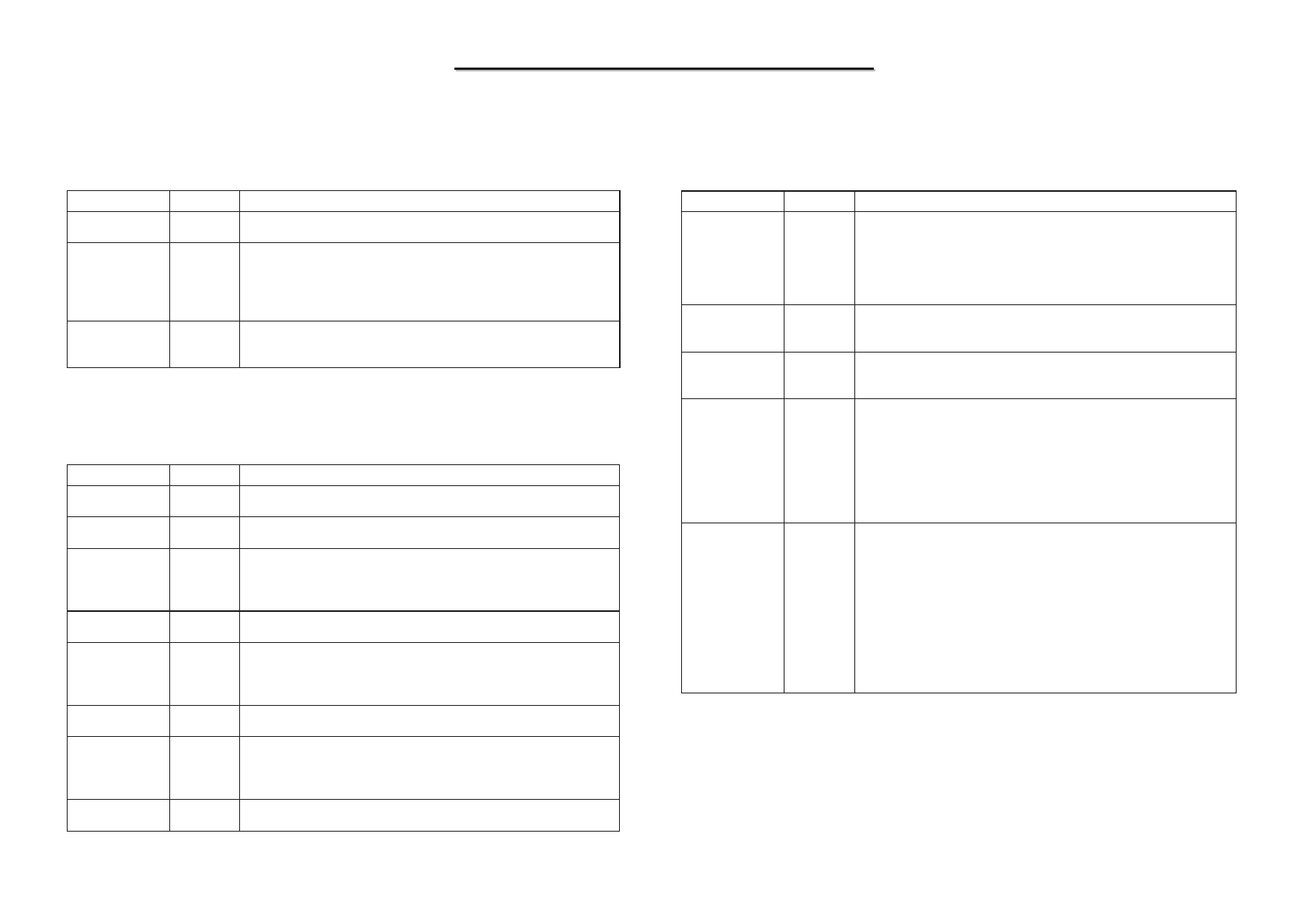

Digital Video Output C (DVOC) Port Signal Descriptions

Name Type Description

DVOCD[11:0]

O

DVO

DVOC Data: This data bus is used to drive 12-bit RGB data on each

edge of the differential clock signals, DVOCCLK and DVOCCLK#.

This provides 24-bits of data per clock period. In dual channel mode,

this provides the upper 12-bits of pixel data.

DVOCD[11:0] should be left as left as NC (“Not Connected”) if not

used.

DVOCHSYNC

O

DVO

Horizontal Sync: HSYNC signal for the DVOC interface.

DVOCHSYNC should be left as left as NC (“Not Connected”) if not

used.

DVOCVSYNC

O

DVO

Vertical Sync: VSYNC signal for the DVOC interface.

DVOCVSYNC should be left as left as NC (“Not Connected”) if the

signal is NOT used when using internal graphics device.

DVOCBLANK#

O

DVO

Flicker Blank or Border Period Indication: DVOCBLANK# is a

programmable output pin driven by the GMCH.

When programmed as a blank period indication, this pin indicates

active pixels excluding the border. When programmed as a border

period indication, this pin indicates active pixel including the border

pixels.

DVOCBLANK# should be left as left as NC (“Not Connected”) if not

used.

DVOCFLDSTL

I

DVO

TV Field and Flat Panel Stall Signal. This input can be

programmed to be either a TV Field input from the TV encoder or

Stall input from the flat panel.

DVOC TV Field Signal: When used as a Field input, it synchronizes

the overlay field with the TV encoder field when the overlay is

displaying an interleaved source.

DVOC Flat Panel Stall Signal: When used as the Stall input, it

indicates that the pixel pipeline should stall one horizontal line. The

signal changes during horizontal blanking. The panel fitting logic,

when expanding the image vertically, uses this.

DVOCFLDSTL needs to be pulled down if not used.

DVOB and DVOC Port Common Signal Descriptions

Name Type Description

DVOBCINTR#

I

DVO

DVOBC Interrupt: This pin is used to signal an interrupt, typically

used to indicate a hot plug or unplug of a digital display.

ADDID[7:0]

I

DVO

ADDID[7:0]: These pins are used to communicate to the Video BIOS

when an external device is interfaced to the DVO port.

Note: Bit[7] needs to be strapped low when an on-board DVO device

is present.

The other pins should be left as NC.

DVODETECT

I

DVO

DVODETECT: This strapping signal indicates to the GMCH

whether a DVO device is present or not. When a DVO device is

connected, then DVODETECT = 0.

Analog CRT Display Signal Descriptions

Pin Name Type Description

VSYNC

O

CMOS

CRT Vertical Synchronization: This signal is used as the vertical

sync signal.

HSYNC

O

CMOS

CRT Horizontal Synchronization: This signal is used as the

horizontal sync signal.

RED

O

Analog

Red (Analog Video Output): This signal is a CRT Analog video

output from the internal color palette DAC. The DAC is designed for

a 37.5-§Ù equivalent load on each pin (e.g., 75-§Ù resistor on the

board, in parallel with the 75-§Ù CRT load).

RED#

O

Analog

Red# (Analog Output): Tied to ground.

GREEN

O

Analog

Green (Analog Video Output): This signal is a CRT analog video

output from the internal color palette DAC. The DAC is designed for

a 37.5-§Ù equivalent load on each pin (e.g.,75-§Ù resistor on the

board, in parallel with the 75- §Ù CRT load).

GREEN#

O

Analog

Green# (Analog Output): Tied to ground.

BLUE

O

Analog

Blue (Analog Video Output) : This signal is a CRT Analog video

output from the internal color palette DAC. The DAC is designed for

a 37.5-§Ù equivalent load on each pin (e.g., 75-

ohm resistor on the board, in parallel with the 75-§Ù CRT load).

BLUE#

O

Analog

Blue# (Analog Output): Tied to ground.

5.2 Intel 855GM/GME North Bridge(8)

MiTac Secret

Confidential Document