8050

8050

D N/B Maintenance

D N/B Maintenance

80

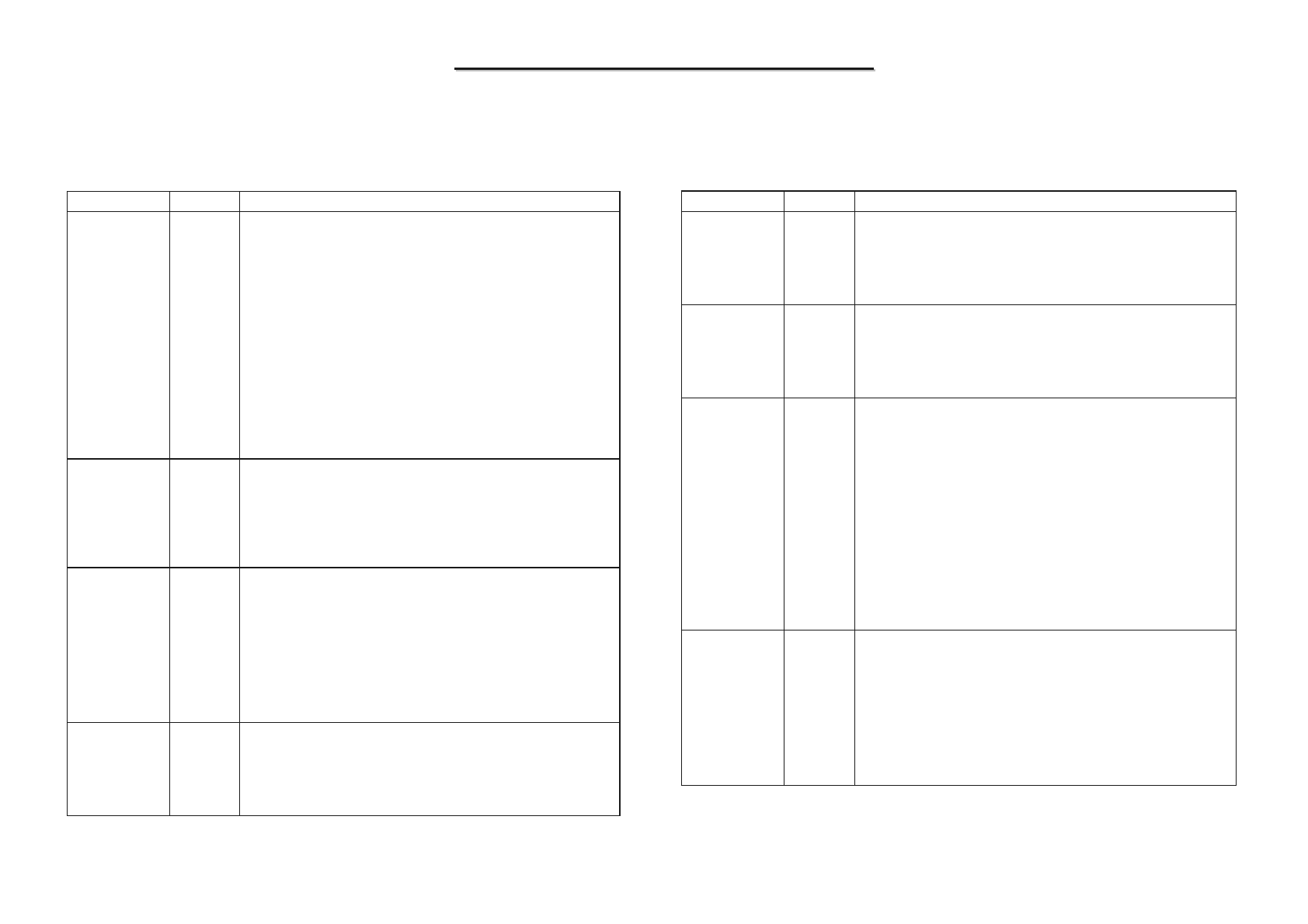

AGP/PCI Signals-Semantics Descriptions (Continued)

Signal Name Type Description

GTRDY#

I/O

AGP

G_TRDY#: Target Ready.

During PIPE# and SBA Operation: Not used while enqueueing

requests via AGP SBA and PIPE#, but used during the data phase of

PIPE# and SBA transactions.

During FRAME# Operation: G_TRDY# is an input when the

GMCH acts as an AGP initiator and is an output when the GMCH

acts as a FRAME#-based AGP target. The assertion of G_TRDY#

indicates the target’s ability to complete the current data phase of the

transaction.

During Fast Write Operation: In Fast Write mode, G_TRDY#

indicates the AGP-compliant target is ready to receive write data for

the entire transaction (when the transfer size is less than or equal to 32

bytes) or is ready to transfer the initial or

subsequent block (32 bytes) of data when the transfer size is greater

than 32 bytes. The target is allowed to insert wait states after each

block (32 bytes) is transferred on write transactions.

GSTOP#

I/O

AGP

G_STOP#: Stop.

During PIPE# and SBA Operation: This signal is not used during

PIPE# or SBA operation.

During FRAME# Operation: G_STOP# is an input when the

GMCH acts as a FRAME#-

b

ased AGP initiator and is an output when

the GMCH acts as a FRAME#-based AGP target. G_STOP# is used

for disconnect, retry, and abort sequences on the AGP interface.

GDEVSEL#

I/O

AGP

G_ DEVSEL#: Device Select.

During PIPE# and SBA Operation: This signal is not used during

PIPE# or SBA operation.

During FRAME# Operation: G_DEVSEL#, when asserted,

indicates that a FRAME#-based AGP target device has decoded its

address as the target of the current access. The GMCH asserts

G_DEVSEL# based on the DDR SDRAM

address range being accessed by a PCI initiator. As an input,

G_DEVSEL# indicates whether the AGP master has recognized a

PCI cycle to it.

GREQ#

I

AGP

G_REQ#: Request.

During SBA Operation: This signal is not used during SBA

operation.

During PIPE# and FRAME# Operation: G_REQ#, when asserted,

indicates that the AGP master is requesting use of the AGP interface

to run a FRAME#- or PIPE#-based operation.

Signal Name Type Description

GGNT#

O

AGP

G_GNT#: Grant.

During SBA, PIPE# and FRAME# Operation: G_GNT#, along

with the information on the ST[2:0] signals (status bus), indicates

how the AGP interface will be used next. Refer to the

AGP Interface

Specification, Revision 2.0

for further explanation

of the ST[2:0] values and their meanings.

GAD[31:0]

I/O

AGP

G_AD[31:0]: Address/Data Bus.

During PIPE# and FRAME# Operation: The G_AD[31:0] signals

are used to transfer both address and data information on the AGP

interface.

During SBA Operation: The G_AD[31:0] signals are used to

transfer data on the AGP interface.

GCBE#[3:0]

I/O

AGP

Command/Byte Enable.

During FRAME# Operation: During the address phase of a

transaction, the G_CBE[3:0]# signals define the bus command.

During the data phase, the G_CBE[3:0]# signals are used as byte

enables. The byte enables determine which byte lanes carry

meaningful data. The commands issued on the G_CBE# signals

during FRAME#-based AGP transactions are the same G_CBE#

command described in the PCI 2.2 specification.

During PIPE# Operation: When an address is enqueued using

PIPE#, the C/BE# signals carry command information. The command

encoding used during PIPE#-based AGP is

different than the

command encoding used during FRAME#-based AGP cycles (or

standard PCI cycles on a PCI bus).

During SBA Operation: These signals are not used during SBA

operation.

GPAR

I/O

AGP

Parity.

During FRAME# Operation: G_PAR is driven by the GMCH when

it acts as a FRAME#-based AGP initiator during address and data

phases for a write cycle, and during the address phase for a read

cycle. G_PAR is driven by the GMCH when it acts as a

FRAME#-based AGP target during each data phase of a

FRAME#-based AGP memory read cycle. Even parity is generated

across G_AD[31:0] and G_CBE[3:0]#.

During SBA and PIPE# Operation: This signal is not used during

SBA and PIPE# operation.

PCIRST# from the ICH4-M is assumed to be connected to RSTIN# and is used to reset AGP interface

logic within the GMCH. The AGP agent will also typically use PCIRST# provided by the ICH4-M as

an input to reset its internal logic.

5.2 Intel 855GM/GME North Bridge(6)

ATP/PCI Signals-Semantics Descriptions(Continued)

MiTac Secret

Confidential Document