8050

8050

D N/B Maintenance

D N/B Maintenance

90

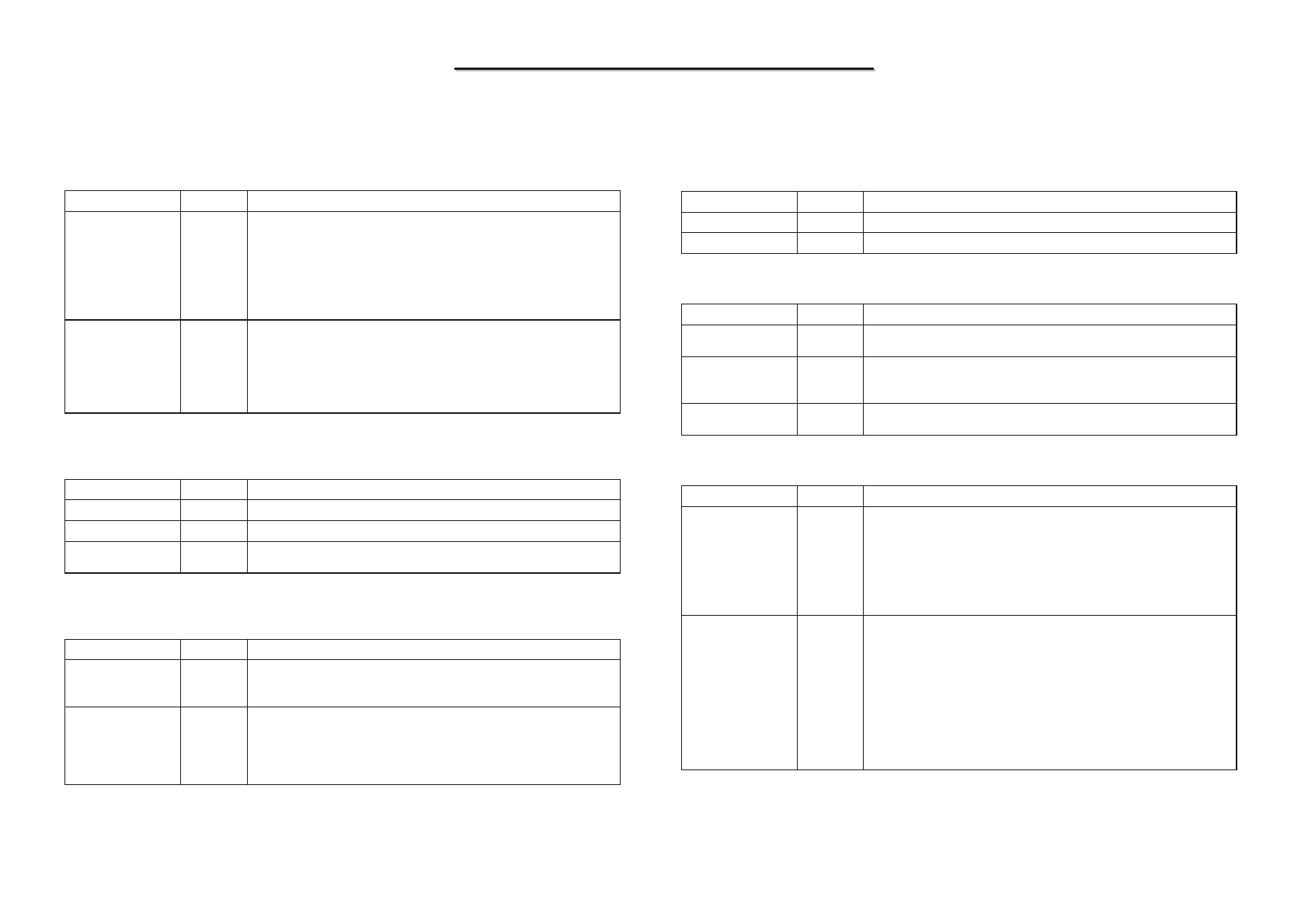

Processor Interface Signals (Continued)

Signal Name Type Description

CPUPWRGD

OD CPU Power Good: This signal should be connected to the

processor’s PWRGOOD input. To allow for Intel ® SpeedStep™

technology support, this signal is kept high during an Intel

SpeedStep technology state transition to prevent loss of processor

context. This is an open-drain output signal (external pull-up

resistor required) that represents a logical AND of the ICH4’s

PWROK and VGATE / VRMPWRGD signals.

DPSLP#

O Deeper Sleep: This signal is asserted by the ICH4 to the processor.

When the signal is low, the processor enters the Deeper Sleep state

by gating off the processor Core clock inside the processor. When

the signal is high (default), the processor is not in the Deeper Sleep

state. This signal behaves identically to the STP_CPU# signal, but

at the processor voltage level.

SMBus Interface Signals

Signal Name Type Description

SMBDATA

I/OD SMBus Data: External pull-up is required.

SMBCLK

I/OD SMBus Clock: External pull-up is required.

SMBALERT#/

GPIO[11]

I SMBus Alert: This signal is used to wake the system or generate

SMI#. If not used for SMBALERT#, it can be used as a GPI.

System Management Interface Signals

Signal Name Type Description

INTRUDER#

I Intruder Detect: Can be set to disable system if box detected open.

This signal’s status is readable, so it can be used like a GPI if the

Intruder Detection is not needed.

SMLINK[1:0]

I/OD System Management Link: SMBus link to optional external

system management ASIC or LAN controller. External pull-ups are

required.

Note that SMLINK[0] corresponds to an SMBus Clock signal, and

SMLINK[1] corresponds to an SMBus Data signal.

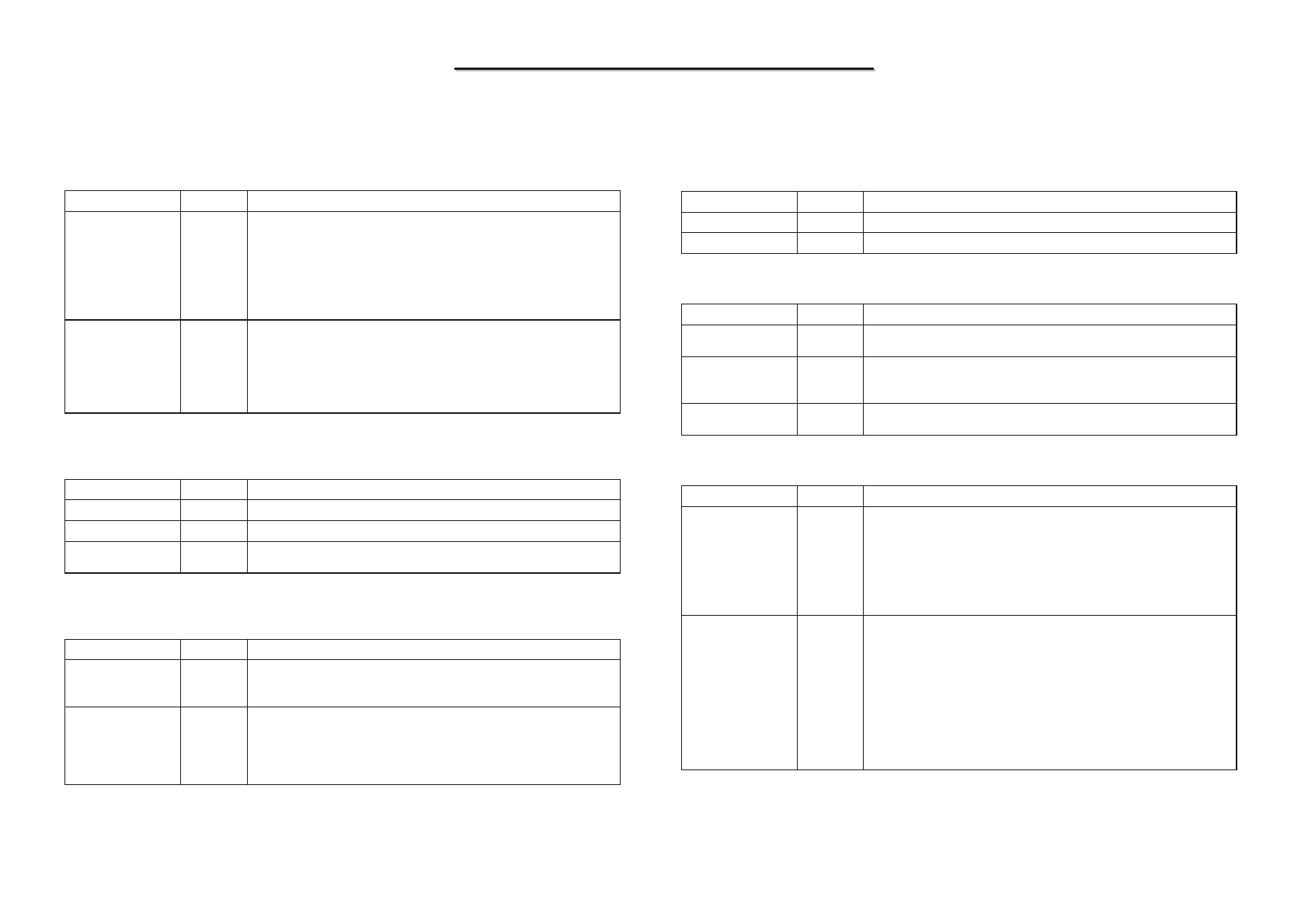

Real Time Clock Interface Signals

Signal Name Type Description

RTCX1

Special Crystal Input 1: This signal is connected to the 32.768 kHz crystal.

RTCX2

Special Crystal Input 2: This signal is connected to the 32.768 kHz crystal.

Other Clock Signals

Signal Name Type Description

CLK14

I Oscillator Clock: Used for 8254 timers. It runs at 14.31818 MHz.

This clock is permitted to stop during S1-M (or lower) states.

CLK48

I 48 MHz Clock: This clock is used to run the USB controller. It runs

at 48 MHz. This clock is permitted to stop during S1-M (or lower)

states.

CLK66

I 66 MHz Clock: This is used to run the hub interface. It runs at 66

MHz. This clock is permitted to stop during S1-M (or lower) states.

Miscellaneous Signals

Signal Name Type Description

SPKR

O Speaker: The SPKR signal is the output of counter 2 and is

internally “ANDed” with Port 61h bit 1 to provide Speaker Data

Enable. This signal drives an external speaker driver device, which

in turn drives the system speaker. Upon PCIRST#, its output state is

0.

NOTE: SPKR is sampled at the rising edge of PWROK as a

functional strap.

RTCRST#

I RTC Reset: When asserted, this signal resets register bits in the

RTC well and sets the RTC_PWR_STS bit (bit 2 in

GEN_PMCON3 register).

NOTES:

1. Clearing CMOS in an ICH4-

ased platform can be done by using

a jumper on RTCRST# or GPI, or using SAFEMODE strap.

Implementations should not attempt to clear CMOS by using a

jumper to pull VccRTC low.

2. Unless entering the XOR Chain Test Mode, the RTCRST# input

must always be high when all other RTC power planes are on.

5.3 Intel 82801DBM I/O Controller Hub 4 Mobile (ICH4-M)(7)

MiTac Secret

Confidential Document