113

80

80

50QMA

50QMA

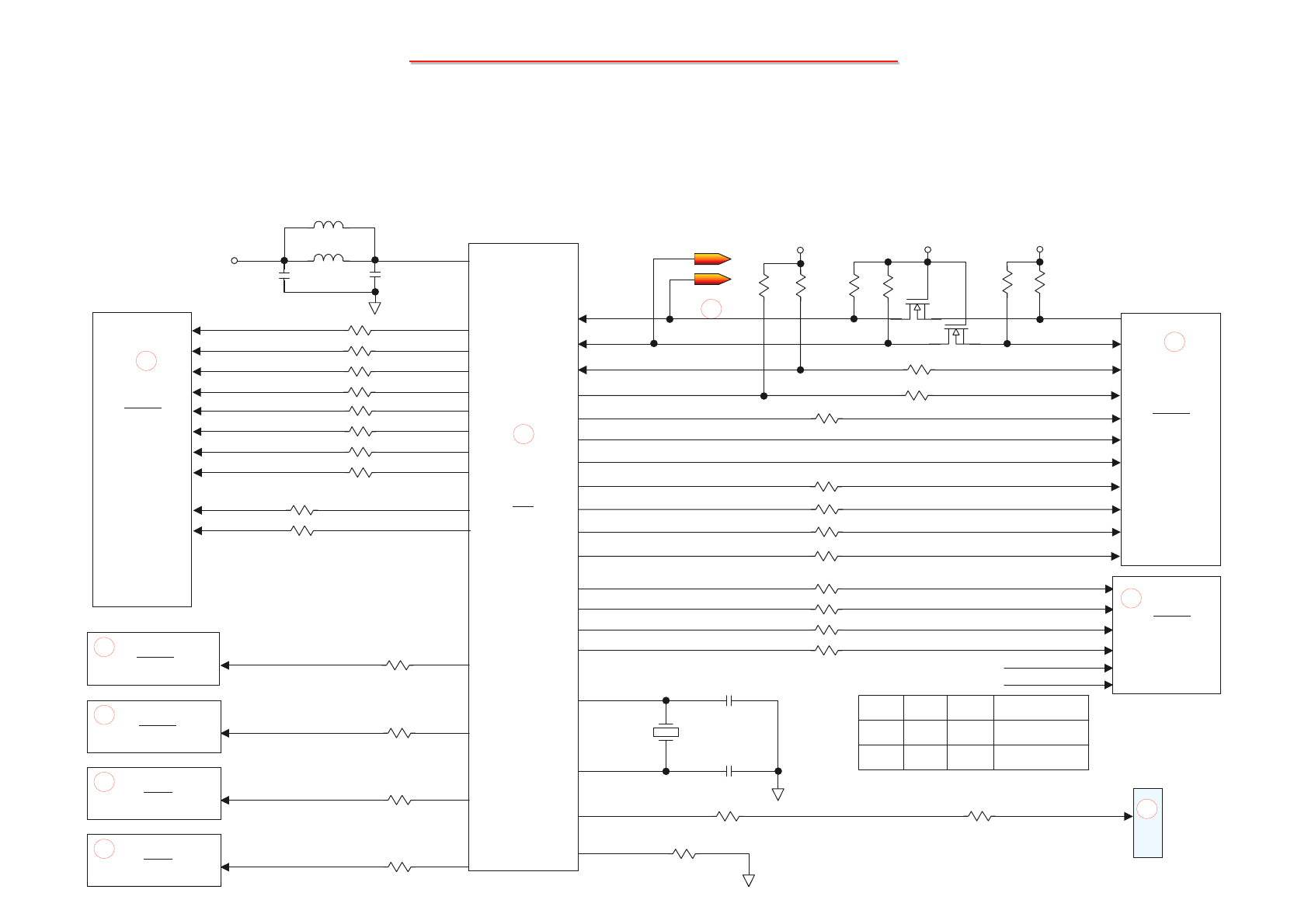

N/B Maintenance

N/B Maintenance

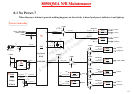

U13

W83L950D

P23

56PCICLK_KBC70

R114

33

U709

South Bridge

ICH6-M

P11

46

8

SMBCLK

SMB_CLK

PCICLK_ICH

R207

2.2K

R206

2.2K

+VDD3S

To J714,J713

P8

47 SMBDATA

SMB_DATA

33R93

R131 12.1

52

14M_ICH

12

CLK_USB48

54

24

STOP_PCI#

STOP_CPU#

CLK_ICH

55

33R98

R80 33

R97 33

R96 33

26

27

CLK_ICH#

CLK_SATA

CLK_SATA#

25

33R95

Q13

2N7002

G

S

D

Q14

2N7002

G

S

D

+3VS

R144

10K

R142

10K

PCICLK_F0

R103

10K

+3VS

FS_A

R76

10K

CLK_PCI_STOP#

CLK_CPU_STOP#

R127 33

R126 33

44

43

HCLK_CPU

HCLK_CPU#

R123 33

R122 33

36

35

CLK_ITP_CPU

CLK_ITP_CPU#

R111 33

R113 33

31

30

R125 33

R124 33

41

40

HCLK_MCH

HCLK_MCH#

CLK_GMCH

CLK_GMCH#

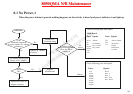

****** System Clock Check ******

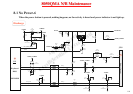

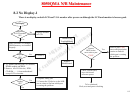

8.2 No Display-2

U711

CPU

DOTHAN

P2

49

50

X1

14.318MHz

C97

56P

C98

56P

21

U7

Clock

Generator

ICS954226

P9

U710

North Bridge

GMCH

P4

39

R136 475

U715

CB712

P18

R94 33

5

PCICLK_CARD

J716

P20

PCICLK_MINIPCI 25

R92 33

R710 0

9

U717

RTL8100CL

P15

4PCICLK_LAN28

R104

33

L32

120Z/100M

+3VS

C80

2.2µ

C78

2.2µ

L31

120Z/100M

+3VS_CLK

U14

SST49LF004A

P24

3PCICLK_FWH31

R105

33

R99 33

R87 33

R101 33

R100 33

17

18

14

15

DREFSSCLK

DREFSSCLK#

DREFCLK

DREFCLK#

133 MHzHLL

100 MHz (Default)HLH

BCLK FrequencyFS_AFS_BFS_C

R71 1K

R72 1K

16

53

CFG1

CFG2

FS_B

FS_C

HBSEL0

HBSEL1

MiTac Secret

Confidential Document