84

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

5.1 Intel 915PM North Bridge(7)

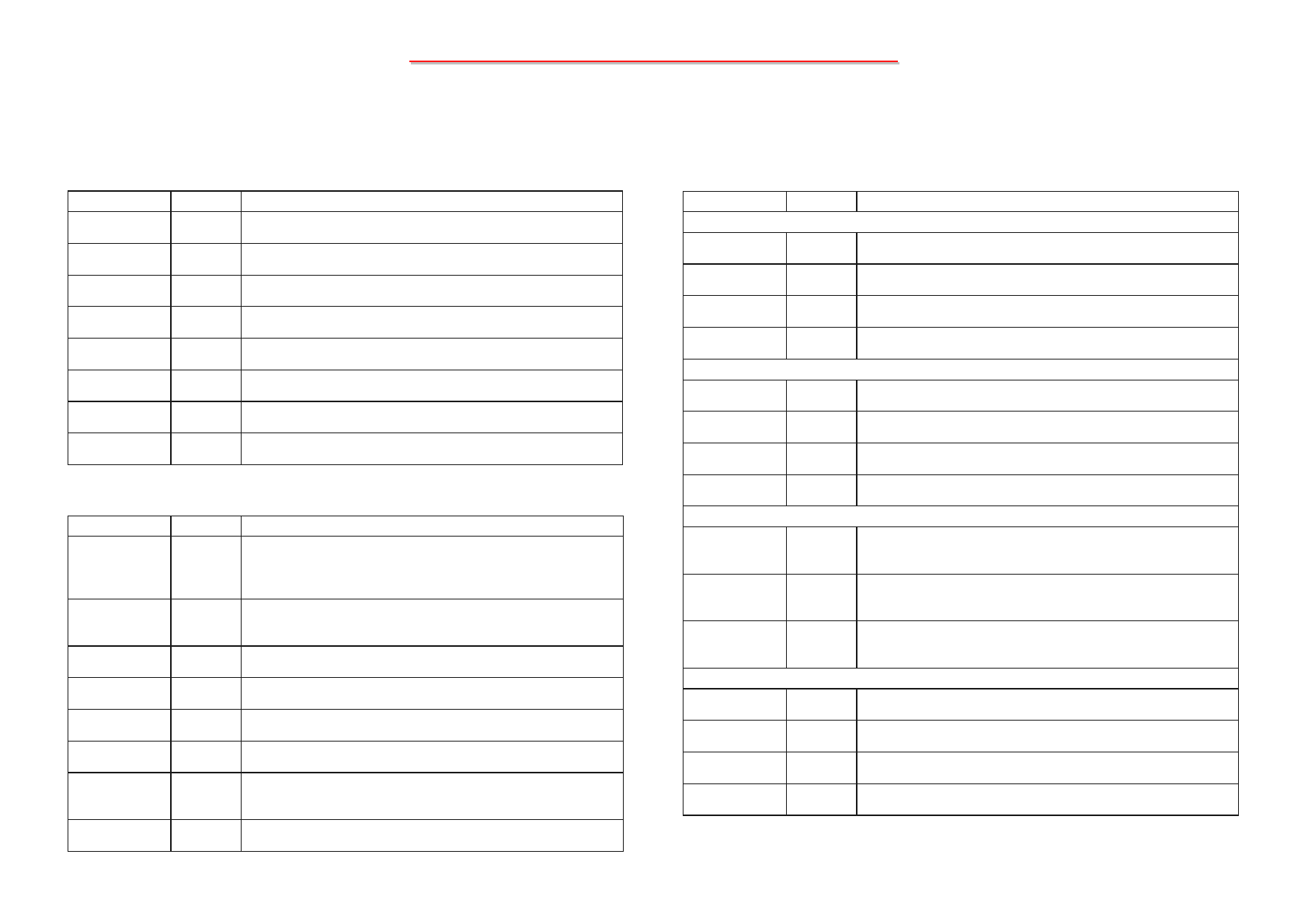

LVDS Signals

Signal Name Type Description

LDVS Channel A

LADATAP[2:0] I/O

LVDS

Channel A differential data output - positive

LADATAN[2:0] I/O

LVDS

Channel A differential data output –negative

LACLKP

I/O

LVDS

Channel A differential clock output – positive

LACLKN I/O

LVDS

Channel A differential clock output – negative

LDVS Channel B

LBDATAP[2:0] I/O

LVDS

Channel B differential data output – positive

NOTE: Signals do not exist in Intel 915GMS.

LBDATAN[2:0] I/O

LVDS

Channel B differential data output –negative

NOTE: Signals do not exist in Intel 915GMS.

LBCLKP I/O

LVDS

Channel B differential clock output – positive

NOTE: Signals do not exist in Intel 915GMS.

LBCLKN I/O

LVDS

Channel B differential clock output – negative

NOTE: Signals do not exist in Intel 915GMS.

LFP Panel power and backlight control

LVDD_EN O

HVCMOS

LVDS panel power enable: Panel power control enable control.

This signal is also called VDD_DBL in the CPIS specification and is

used to control the VDC source to the panel logic.

LBKLT_EN O

HVCMOS

LVDS backlight enable: Panel backlight enable control.

This signal is also called ENA_BL in the CPIS specification and is

used to gate power into the backlight circuitry.

LBKLT_CRTL O

HVCMOS

Panel backlight brightness control: Panel brightness control.

This signal is also called VARY_BL in the CPIS specification and is

used as the PWM Clock input signal.

LVDS Reference signals

LIBG I/O

Ref

LVDS Reference Current. –

1.5 kΩ Pull down resistor needed

LVREFH

I

Ref

Reserved. - No connect.

LVREFL I

Ref

Reserved. - No connect.

LVBG O

A

Reserve. - No connect

Note: LVDS Channel B interface is not supported and do not exist for Intel 915GMS

DDR SDRAM Reference and Compensation

Signal Name Type Description

SMRCOMPN I/O

A

System Memory RCOMP N:

Buffer compensation

This signal is powered by the System Memory rail (2.5 V for DDR,

1.8 V for DDR2).

SMRCOMPP I/O

A

System Memory RCOMP P:

Buffer compensation

This signal is powered by the System Memory rail

SMXSLEWIN I

A

X Buffer Slew Rate Input control.

SMXSLEWOUT O

A

X Buffer Slew Rate Output control.

SMYSLEWIN

I

A

Y Buffer Slew Rate Input control.

SMYSLEWOUT O

A

Y Buffer Slew Rate Output control.

SMVREF[1:0] I

A

SDRAM Reference Voltage:

Reference voltage inputs for each DQ, DQS, & RCVENIN#.

Also used during ODT RCOMP.

SMOCDCOMP[1

:0]

I

A

On-Die DRAM OCD driver compensation

OCD compensation

Display Data Channel (DDC) and GMBUS Support

Signal Name Type Description

LCTLA_CLK I/O

COD

I2C Based control signal (Clock) for External SSC clock chip

control –

LCTLB_DATA I/O

COD

I2C Based control signal (Data) for External SSC clock chip control –

DDCCLK I/O

COD

CRT DDC clock monitor control support

DDCDATA I/O

COD

CRT DDC Data monitor control support

LDDC_CLK I/O

COD

EDID support for flat panel display

LDDC_DATA

I/O

COD

EDID support for flat panel display

SDVOCTRL_CL

K

I/O

COD

I2C Based control signal (Clock) for SDVO device

SDVOCTRL_DA

TA

I/O

COD

I2C Based control signal (Data) for SDVO device

MiTac Secret

Confidential Document