97

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

5.2 Intel ICH6-M South Bridge(10)

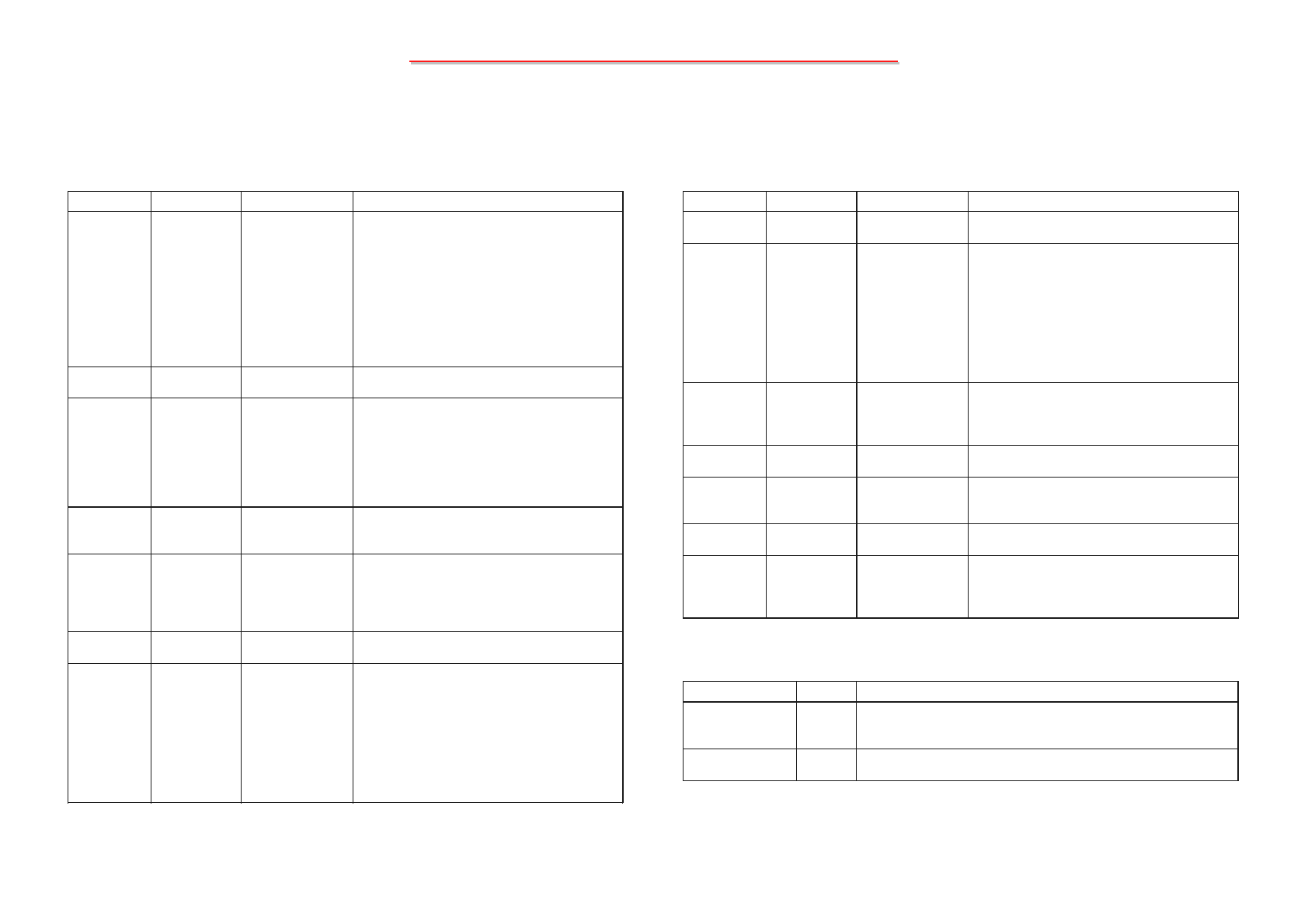

Functional Strap Definitions 1

Signal Usage When Sampled Description

GNT[6]#/

GPO[16]

Top-Block Swa

p

Override

Rising Edge of

PWROK

The signal has a weak internal pull-up. If the

signal is sampled low, this indicates that the

system is strapped to the “top-block swap” mode

(ICH6 inverts A16 for all cycles targeting FWH

BIOS space). The status of this strap is readable

via the Top Swap bit (Chipset Configuration

Registers:Offset 3414h:bit 0). Note that software

will not be able to clear the Top-Swap bit until

the system is rebooted without GNT6# being

pulled down.

LINKALERT

#

Reserved This signal requires an external pull-up resistor.

SPKR No Reboot Rising Edge

ofPWROK

The signal has a weak internal pull-down. If the

signal is.sampled high, this indicates that the

system is strapped to.the “No Reboot” mode

(ICH6 will disable the TCO Timer. system

reboot feature). The status of this strap is

readable. via the NO REBOOT bit (Chipset

Configuration. Registers:Offset 3410h:bit 5).

INTVRMEN IntegratedVccS

u

1_5VRM

Enable/Disabl

e

Always This signal enables integrated VccSus1_5 VRM

when.sampled high.

GPIO[25] Integrated

Vcc2_5 VRM

Enable/ Disabl

e

Rising Edge of

RSMRST#

This signal enables integrated Vcc2_5 VRM

when sampled low. This signal has a weak

internal pull-up during RSMRST# and is

disabled within 100 ms after RSMRST#

de-asserts.

EE_CS Reserved This signal has a weak internal pull-down.

NOTE: This signal should not be pulled high.

GNT[5]#/

GPO[17]

Boot BIOS

Destination

Selection

Rising Edge of

PWROK

This signal has a weak internal pull-up. Allows

for select memory ranges to be forwarded out the

PCI Interface as opposed to the Firmware Hub.

When sampled high, destination is LPC. Also

controllable via Boot BIOS Destination bit

(Chipset Configuration Registers:Offset

3410h:bit 3).

NOTE: This functionality intended for

debug/testing only.

Functional Strap Definitions 1 (Continued)

Signal Usage When Sampled Description

EE_DOUT Reserved This signal has a weak internal pull-up.

NOTE: This signal should not be pulled low.

ACZ_SDOU

T

XOR Chain

Entrance / PCI

Express* Port

Configu-ratio

n

bit 1

Rising Edge of

PWROK

Allows entrance to XOR Chain testing when

TP[3] pulled low at rising edge of PWROK. See

Chapter 24 for XOR Chain functionality

information.

When TP[3] not pulled low at rising edge of

PWROK, sets bit 1 of RPC.PC (Chipset

Configuration Registers:Offset 224h). See

Section 7.1.30 for details.

This signal has a weak internal pull-down.

ACZ_SYNC PCI Express Po

r

Configu-ratio

n

bit 0

Rising Edge of

PWROK

This signal has a weak internal pull-down.

Sets bit 0 of RPC.PC (Chipset Configuration

Registers: Off set 224h). See Section 7.1.30 for

details.

TP[1] Reserved This signal has a weak internal pull-down.

NOTE: This signal should not be pulled high.

SATALED# Reserved This signal has a weak internal pull-up enabled

only when PLTRST# is asserted.

NOTE: This signal should not be pulled low.

REQ[4:1]# XOR Chain

Selection

Rising Edge of

PWROK

See Chapter 24 for functionality information.

TP[3] XOR Chain

Entrance

Rising Edge of

PWROK

See Chapter 24 for functionality information.

This signal has a weak internal pull-up.

NOTE: This signal should not be pulled low

unless using XOR Chain testing.

Real Time Clock Interface

Name Type Description

RTCX1

Special Crystal Input 1: This signal is connected to the 32.768 kHz crystal.

If no external crystal is used, then RTCX1 can be driven with the

desired clock rate.

RTCX2

Special Crystal Input 2: This signal is connected to the 32.768 kHz crystal.

If no external crystal is used, then RTCX2 should be left floating.

MiTac Secret

Confidential Document