92

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

5.2 Intel ICH6-M South Bridge(5)

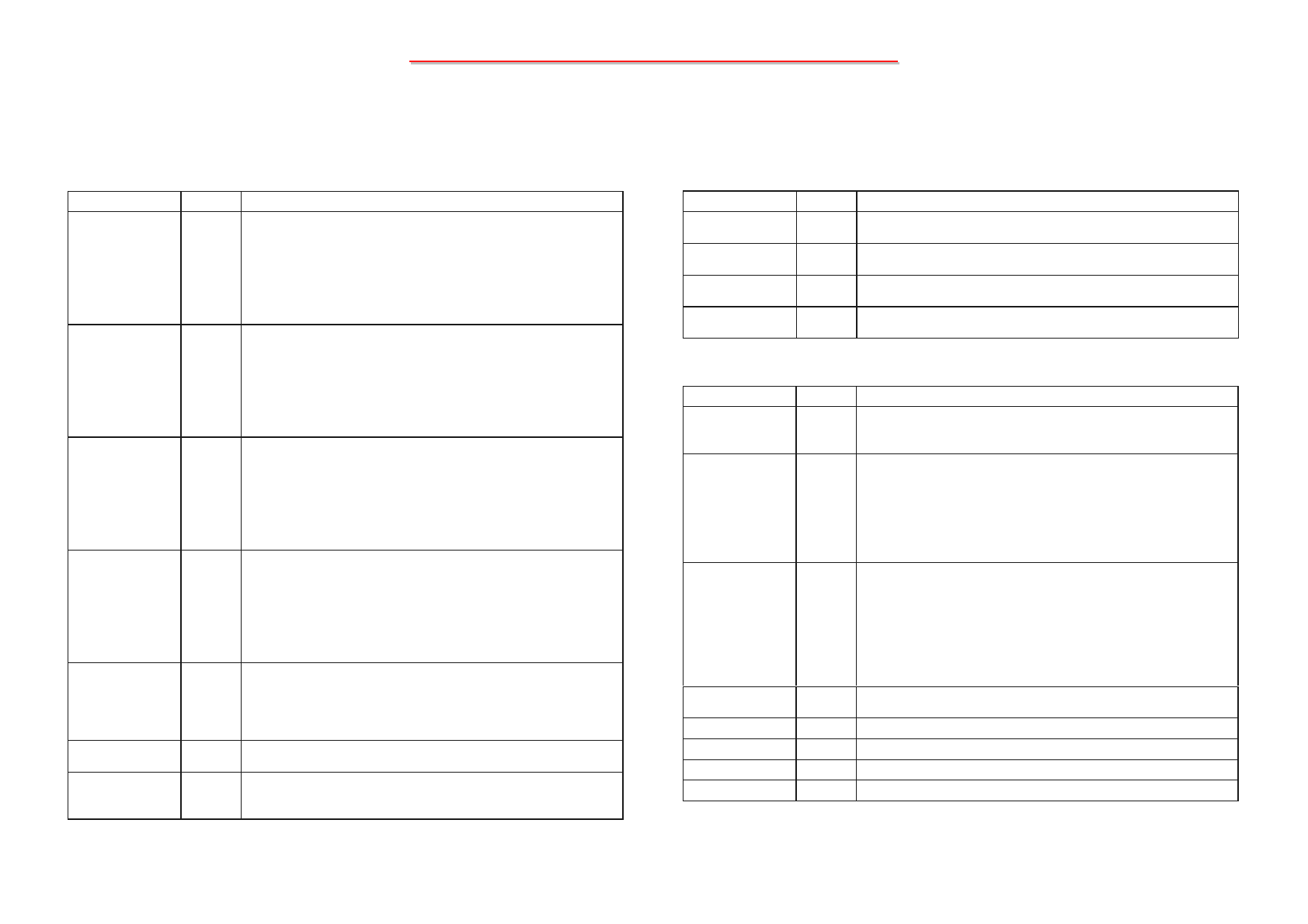

USB Interface Signals

Name Type Description

USBP[0]P,

USBP[0]N,

USBP[1]P,

USBP[1]N

I/O Universal Serial Bus Port [1:0] Differential: These differential pairs

are used to transmit Data/Address/Command signals for ports 0 and 1.

These ports can be routed to UHCI controller #1 or the EHCI

controller.

NOTE: No external resistors are required on these signals. The ICH6

integrates 15 K

Ω?pull-downs and provides an output driver

impedance of 45

Ωwhich requires no external series resistor

USBP[2]P,

USBP[2]N,

USBP[3]P,

USBP[3]N

I/O Universal Serial Bus Port [3:2] Differential: These differential pairs

are used to transmit data/address/command signals for ports 2 and 3.

These ports can be routed to UHCI controller #2 or the EHCI

controller.

NOTE: No external resistors are required on these signals. The ICH6

integrates 15 K

Ω?pull-downs and provides an output driver

impedance of 45

Ωwhich requires no external series resistor

USBP[4]P,

USBP[4]N,

USBP[5]P,

USBP[5]N

I/O

Universal Serial Bus Port [5:4] Differentia

l: These differential pairs

are used to transmit Data/Address/Command signals for ports 4 and 5.

These ports can be routed to UHCI controller #3 or the EHCI

controller.

NOTE: No external resistors are required on these signals. The ICH6

integrates 15 K

Ω?pull-downs and provides an output driver

impedance of 45

Ω

which requires no external series resistor

USBP[6]P,

USBP[6]N,

USBP[7]P,

USBP[7]N

I/O Universal Serial Bus Port [7:6] Differential: These differential pairs

are used to transmit Data/Address/Command signals for ports 6 and 7.

These ports can be routed to UHCI controller #4 or the EHCI

controller.

NOTE: No external resistors are required on these signals. The ICH6

integrates 15 K

Ω

?pull-downs and provides an output driver

impedance of 45

Ω

which requires no external series resistor

OC[3:0]#

OC[4]# / GPI[9]

OC[5]# / GPI[10]

OC[6]# / GPI[14]

OC[7]# / GPI[15]

I Overcurrent Indicators: These signals set corresponding bits in the

USB controllers to indicate that an overcurrent condition has

occurred.

OC[7:4]# may optionally be used as GPIs.

NOTE: OC[7:0]# are not 5 V tolerant.

USBRBIAS

O USB Resistor Bias: Analog connection point for an external resistor.

Used to set transmit currents and internal load resistors.

USBRBIAS#

I USB Resistor Bias Complement: Analog connection point for an

external resistor. Used to set transmit currents and internal load

resistors.

Miscellaneous Signals

Name Type Description

INTVRMEN

I Internal Voltage Regulator Enable: This signal enables the internal

1.5 V Suspend regulator when connected to VccRTC. When

connected to Vss, the internal regulator is disabled

SPKR

O Speaker: The SPKR signal is the output of counter 2 and is internally

“ANDed” with Port 61h bit 1 to provide Speaker Data Enable. This

signal drives an external speaker driver device that in turn drives the

system speaker. Upon PLTRST#, its output state is 0.

NOTE: SPKR is sampled at the rising edge of PWROK as a

functional strap. See Section 2.22.1 for more details. There is a weak

integrated pull-down resistor on SPKR pin.

RTCRST#

I RTC Reset: When asserted, this signal resets register bits in the RTC

well.

NOTES:

1. Unless CMOS is being cleared (only to be done in the G3 power

state), the RTCRST# input must always be high when all other

RTC power planes are on.

2. In the case where the RTC battery is dead or missing on the

platform, the RTCRST# pin must rise before the RSMRST# pin.

TP[0]

I Test Point 0: This signal must have an external pull-up to

VccSus3_3.

TP[1]

O Test Point 1: Route signal to a test point.

TP[2]

O Test Point 2: Route signal to a test point.

TP[3]

I Test Point 3: Route signal to a test point.

TP[4]

O Test Point 4: Route signal to a test point.

EEPROM Interface Signals

Name Type Description

EE_SHCLK

O EEPROM Shift Clock: This signal is the serial shift clock output to

the EEPROM.

EE_DIN

I EEPROM Data In: This signal transfers data from the EEPROM to

the Intel ® ICH6. This signal has an integrated pull-up resistor.

EE_DOUT

O EEPROM Data Out: This signal transfers data from the ICH6 to the

EEPROM.

EE_CS

O EEPROM Chip Select: This is the chip select signal to the

EEPROM.

MiTac Secret

Confidential Document