90

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

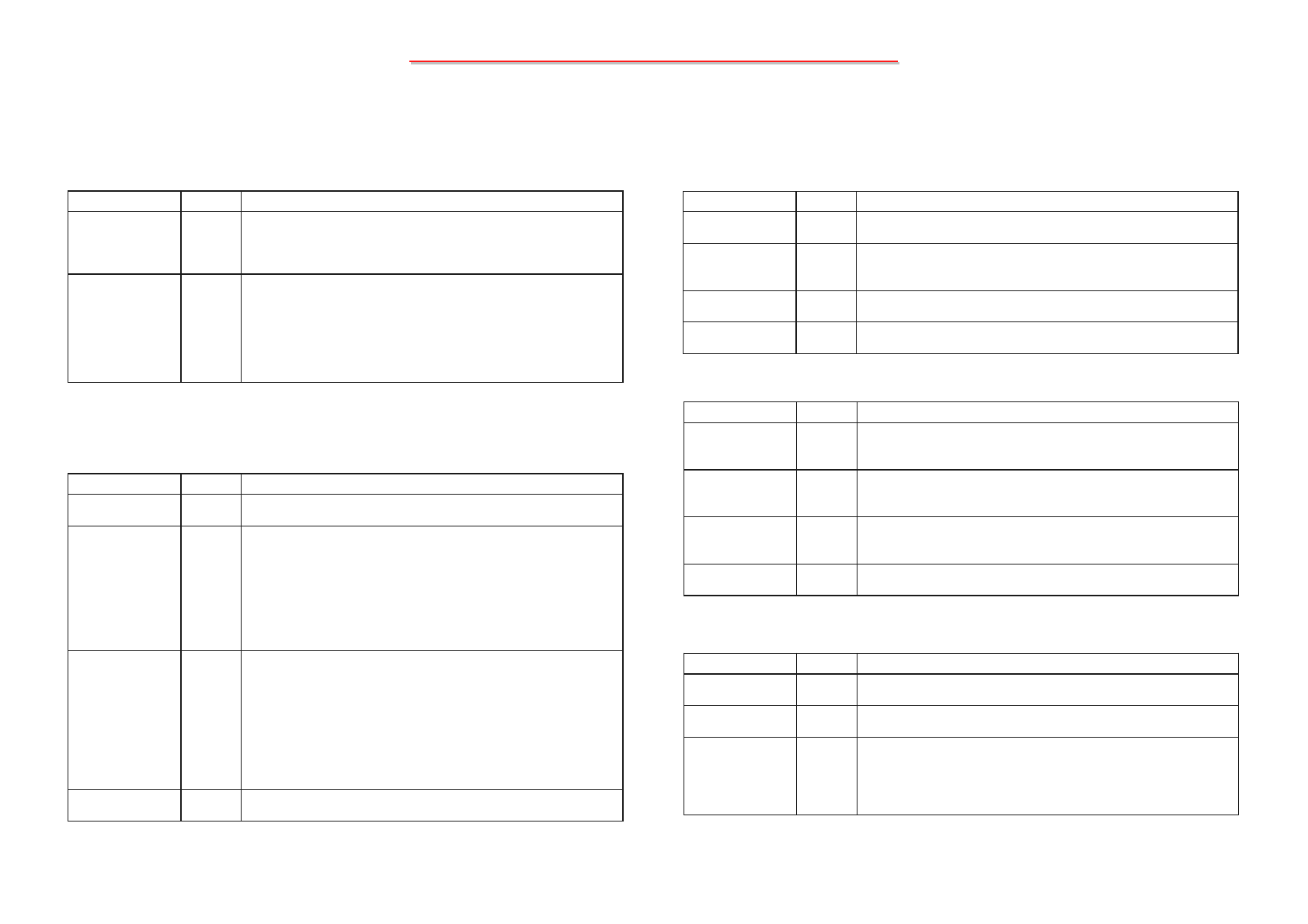

5.2 Intel ICH6-M South Bridge(3)

Serial ATA Interface Signals (Continued)

Name Type Description

SATA[3]GP /

GPI[31]

I Serial ATA 3 General Purpose: Same function as SATA[0]GP,

except for SATA Port 3.

If interlock switches are not required, this pin can be configured as

GPI[31].

SATALED#

OC O

Serial ATA LED:

This is an open-collector output pin driven during

SATA command activity. It is to be connected to external circuitry

that can provide the current to drive a platform LED. When active,

the LED is on. When tri-stated, the LED is off. An external pull-up

resistor to Vcc3_3 is required.

NOTE: An internal pull-up is enabled only during PLTRST#

assertion.

LAN Connect Interface Signals

Name Type Description

LAN_CLK

I LAN I/F Clock: This signal is driven by the LAN Connect

component. The frequency range is 5 MHz to 50 MHz.

LAN_RXD[2:0]

I Received Data: The LAN Connect component uses these signals to

transfer data and control information to the integrated LAN

controller. These signals have integrated weak pull-up resistors.

LAN_TXD[2:0]

O Transmit Data: The integrated LAN controller uses these signals to

transfer data and control information to the LAN Connect component.

LAN_RSTSYNC

O LAN Reset/Sync: The LAN Connect component’s Reset and Sync

signals are multiplexed onto this pin.

Other Clocks

Name Type Description

CLK14

I Oscillator Clock: This clock is used for 8254 timers. It runs at

14.31818 MHz. This clock is permitted to stop during S3 (or lower)

states.

CLK48

I 48 MHz Clock: This clock is used to run the USB controller. IT runs

at 48.000 MHz.

This clock is permitted to stop during S3 (or lower) states.

SATA_CLKP

SATA_CLKN

I 100 MHz Differential Clock: These signals are used to run the

SATA controller. Runs at 100 MHz. This clock is permitted to stop

during S3 (or lower) states.

DMI_CLKP,

DMI_CLKN

I 100 MHz Differential Clock: These signals are used to run the

Direct Media Interface. Runs at 100 MHz.

Interrupt Signals

Name Type Description

SERIRQ

I/O Serial Interrupt Request: This pin implements the serial interrupt

protocol.

PIRQ[D:A]#

OD I PCI Interrupt Requests: In non-APIC mode the PIRQx# signals can

be routed to interrupts 3, 4, 5, 6, 7, 9, 10, 11, 12, 14 or 15 as described

in the Interrupt Steering section. Each PIRQx# line has a separate

Route Control register.

In APIC mode, these signals are connected to the internal I/O APIC in

the following fashion: PIRQA# is connected to IRQ16, PIRQB# to

IRQ17, PIRQC# to IRQ18, and PIRQD# to IRQ19. This frees the

legacy interrupts.

PIRQ[H:E]# /

GPI[5:2]

OD I PCI Interrupt Requests: In non-APIC mode the PIRQx# signals can

be routed to interrupts 3, 4, 5, 6, 7, 9, 10, 11, 12, 14 or 15 as described

in the Interrupt Steering section. Each PIRQx# line has a separate

Route Control register.

In APIC mode, these signals are connected to the internal I/O APIC in

the following fashion: PIRQE# is connected to IRQ20, PIRQF# to

IRQ21, PIRQG# to IRQ22, and PIRQH# to IRQ23. This frees the

legacy interrupts. If not needed for interrupts, these signals can be

used as GPI.

IDEIRQ

I IDE Interrupt Request: This interrupt input is connected to the IDE

drive.

LPC Interface Signals

Name Type Description

LAD[3:0]

/

FWH[3:0]

I/O

LPC Multiplexed Command, Address, Data:

For LAD[3:0],

internal pull-ups are provided.

LFRAME# /

FWH[4]

O LPC Frame: LFRAME# indicates the start of an LPC cycle, or an

abort.

LDRQ[0]#

LDRQ[1]# /

GPI[41]

I LPC Serial DMA/Master Request Inputs: LDRQ[1:0]# are used to

request DMA or bus master access. These signals are typically

connected to external Super I/O device. An internal pull-up resistor is

provided on these signals.

LDRQ[1]# may optionally be used as GPI.

MiTac Secret

Confidential Document