88

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

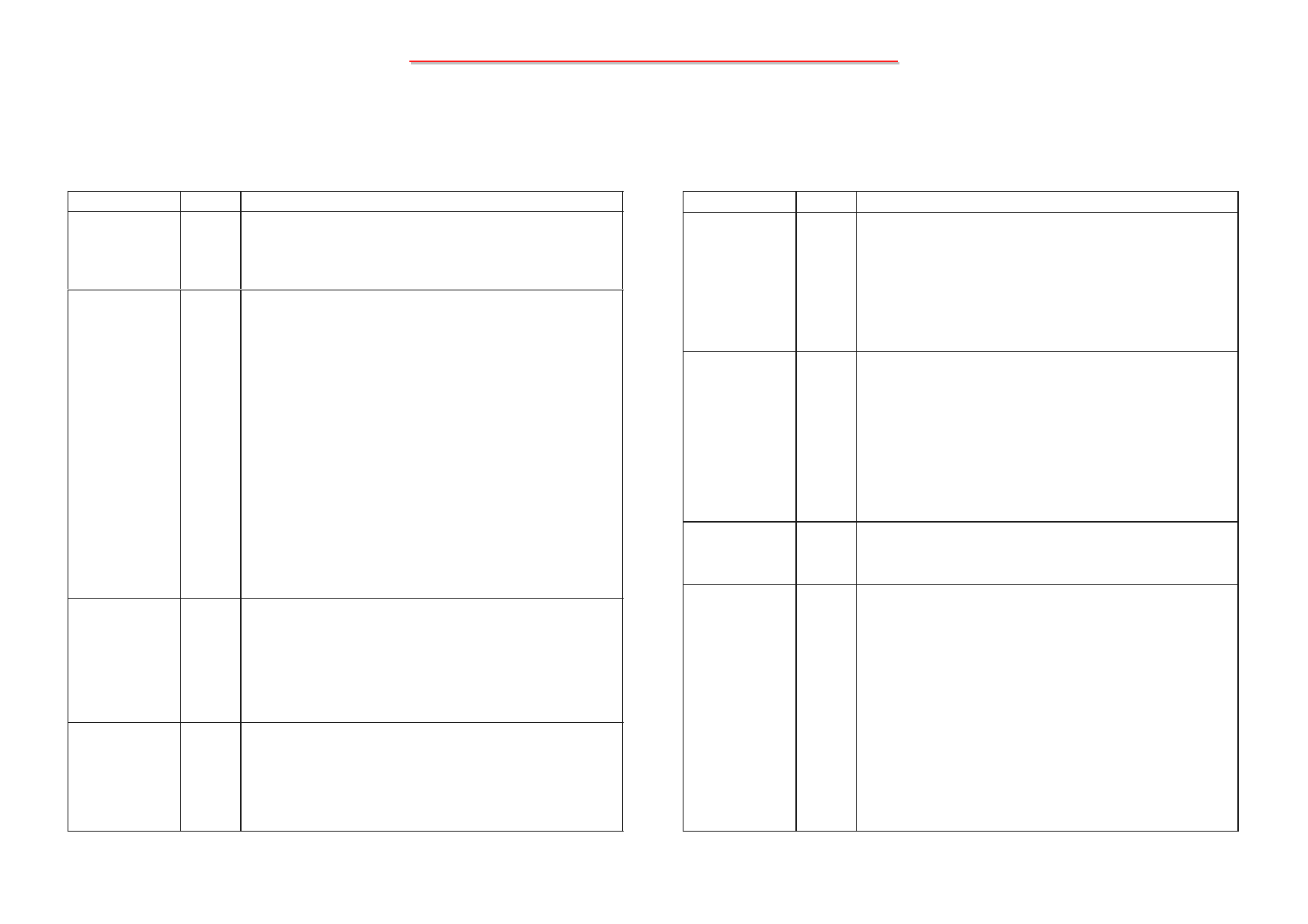

5.2 Intel ICH6-M South Bridge(1)

PCI Interface Signals

Name Type Description

AD[31:0]

I/O PCI Address/Data: AD[31:0] is a multiplexed address and data bus.

During the first clock of a transaction, AD[31:0] contain a physical

address (32 bits). During subsequent clocks, AD[31:0] contain data.

The Intel® ICH6 will drive all 0s on AD[31:0] during the address

phase of all PCI Special Cycles.

C/BE[3:0]#

I/O Bus Command and Byte Enables: The command and byte enable

signals are multiplexed on the same PCI pins. During the address

phase of a transaction,

C/BE[3:0]# define the bus command. During the data phase

C/BE[3:0]# define the Byte Enables.

C/BE[3:0]# Command Type

0000b Interrupt Acknowledge

0001b Special Cycle

0010b I/O Read

0011b I/O Write

0110b Memory Read

0111b Memory Write

1010b Configuration Read

1011b Configuration Write

1100b Memory Read Multiple

1110b Memory Read Line

1111b Memory Write and Invalidate

All command encodings not shown are reserved. The ICH6 does not

decode reserved values, and therefore will not respond if a PCI master

generates a cycle using one of the reserved values.

DEVSEL#

I/O Device Select: The ICH6 asserts DEVSEL# to claim a PCI

transaction. As an output, the ICH6 asserts DEVSEL# when a PCI

master peripheral attempts an access to an internal ICH6 address or an

address destined DMI (main memory or graphics). As an input,

DEVSEL# indicates the response to an ICH6-initiated transaction on

the PCI bus. DEVSEL# is tri-stated from the leading edge of

PLTRST#. DEVSEL# remains tri-stated by the ICH6 until driven by

a target device.

FRAME#

I/O Cycle Frame: The current initiator drives FRAME# to indicate the

beginning and duration of a PCI transaction. While the initiator

asserts FRAME#, data transfers continue. When the initiator negates

FRAME#, the transaction is in the final data phase. FRAME# is an

input to the ICH6 when the ICH6 is the target, and FRAME# is an

output from the ICH6 when the ICH6 is the initiator. FRAME#

remains tri-stated by the ICH6 until driven by an initiator.

PCI Interface Signals (Continued)

Name Type Description

IRDY#

I/O Initiator Ready: IRDY# indicates the ICH6's ability, as an initiator,

to complete the current data phase of the transaction. It is used in

conjunction with TRDY#. A data phase is completed on any clock

both IRDY# and TRDY# are sampled asserted. During a write,

IRDY# indicates the ICH6 has valid data present on AD[31:0].

During a read, it indicates the ICH6 is prepared to latch data. IRDY#

is an input to the ICH6 when the ICH6 is the target and an output

from the ICH6 when the ICH6 is an initiator. IRDY# remains

tri-stated by the ICH6 until driven by an initiator.

TRDY#

I/O Target Ready: TRDY# indicates the ICH6's ability as a target to

complete the current data phase of the transaction. TRDY# is used in

conjunction with IRDY#. A data phase is completed when both

TRDY# and IRDY# are sampled asserted.

During a read, TRDY# indicates that the ICH6, as a target, has placed

valid data on AD[31:0]. During a write, TRDY# indicates the ICH6,

as a target is prepared to latch data. TRDY# is an input to the ICH6

when the ICH6 is the initiator and an output from the ICH6 when the

ICH6 is a target. TRDY# is tri-stated from the leading edge of

PLTRST#. TRDY# remains tri-stated by the ICH6 until driven by a

target.

STOP#

I/O Stop: STOP# indicates that the ICH6, as a target, is requesting the

initiator to stop the current transaction. STOP# causes the ICH6, as an

initiator, to stop the current transaction. STOP# is an output when the

ICH6 is a target and an input when the ICH6 is an initiator.

PAR

I/O Calculated/Checked Parity: PAR uses “even” parity calculated on

36 bits, AD[31:0] plus C/BE[3:0]#. “Even” parity means that the

ICH6 counts the number of one within the 36 bits plus PAR and the

sum is always even. The ICH6 always calculates PAR on 36 bits

regardless of the valid byte enables. The ICH6 generates PAR for

address and data phases and only guarantees PAR to be valid one PCI

clock after the corresponding address or data phase. The ICH6 drives

and tri-states PAR identically to the AD[31:0] lines except that the

ICH6 delays PAR by exactly one PCI clock. PAR is an output during

the address phase (delayed one clock) for all ICH6 initiated

transactions. PAR is an output during the data phase (delayed one

clock) when the ICH6 is the initiator of a PCI write transaction, and

when it is the target of a read transaction. ICH6 checks parity when it

is the target of a PCI write transaction. If a parity error is detected, the

ICH6 will set the appropriate internal status bits, and has the option to

generate an NMI# or SMI#.

MiTac Secret

Confidential Document