79

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

5.1 Intel 915PM North Bridge(2)

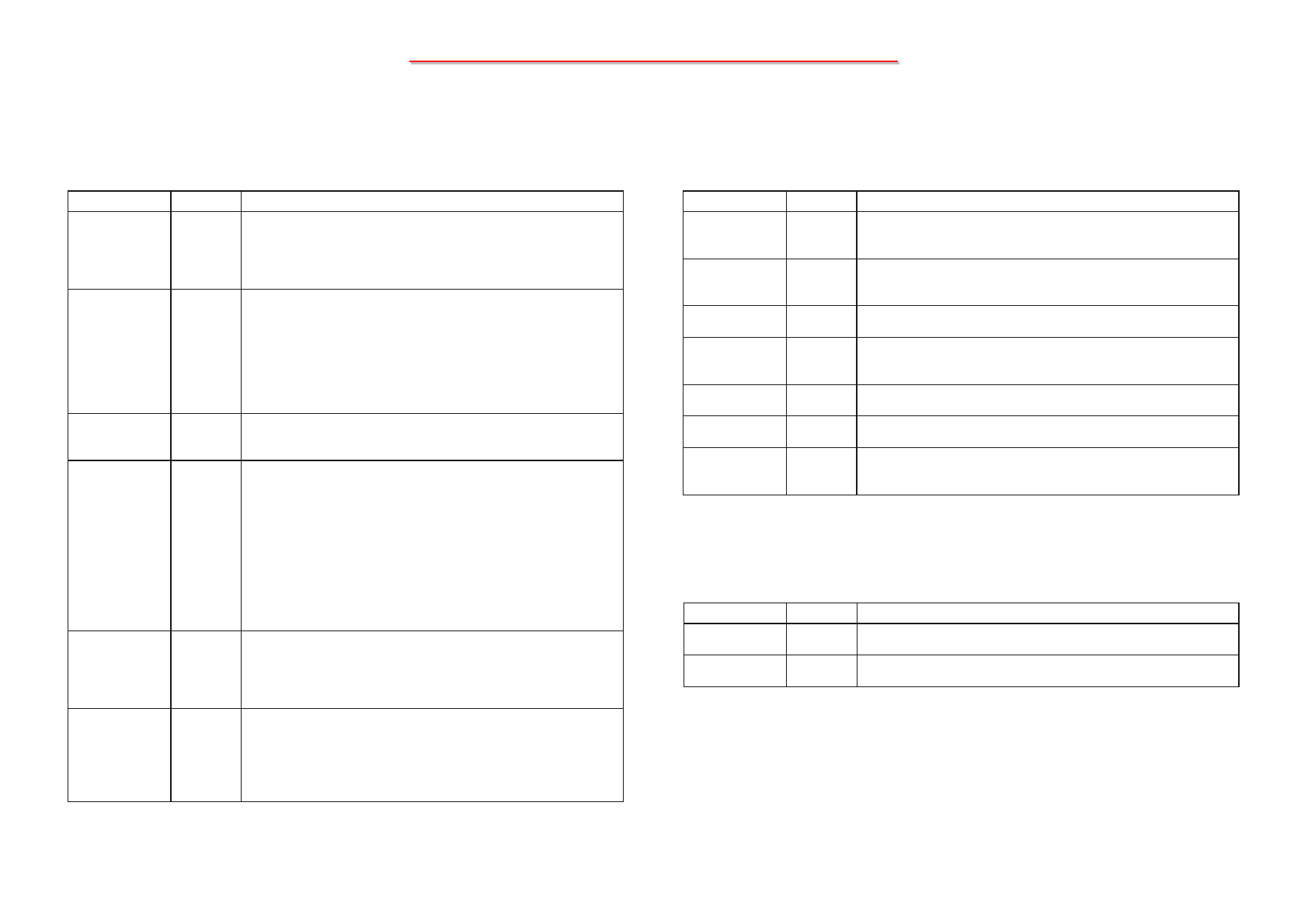

Host Interface Signals (Continued)

Signal Name Type Description

HLOCK# I

AGTL+

Host Lock:

All CPU bus cycles sampled with the assertion of HLOCK# and

HADS#, until the negation of HLOCK# must be atomic, i.e. PCI

Express graphics access to System Memory is allowed when

HLOCK# is asserted by the CPU.

HREQ[4:0]# I/O

AGTL+

2X

Host Request Command:

Defines the attributes of the request. HREQ[4:0]# are transferred at

2x rate.

Asserted by the requesting agent during both halves of the Request

Phase. In the first half the signals define the transaction type to a level

of detail that is sufficient to begin a snoop request. In the second half

the signals carry additional information to define the complete

transaction type.

HTRDY# O

AGTL+

Host Target Ready:

Indicates that the target of the processor transaction is able to enter

the data transfer phase.

HRS[2:0]# O

AGTL+

Host Response Status:

Indicates the type of response according to the following the table:

HRS[2:0]# Response type

000 Idle state

001 Retry response

010 Deferred response

011 Reserved (not driven by GMCH)

100 Hard Failure (not driven by GMCH)

101 No data response

110 Implicit Write back

111 Normal data response

HDPWR# O

AGTL+

Host Data Power:

Used by GMCH to indicate that a data return cycle is pending within

2 HCLK cycles or more. CPU use’s this signal during a read-cycle to

activate the data input buffers in preparation for HDRDY# and the

related data.

HCPUSLP# O

CMOS

Host CPU Sleep:

When asserted in the Stop-Grant state, causes the processor to enter

the Sleep state. During Sleep state, the processor stops providing

internal clock signals to all units, leaving only the Phase-Locked

Loop (PLL) still operating. Processors in this state will not recognize

snoops or interrupts.

Host Interface Reference and Compensation

Signal Name Type Description

HVREF I

A

Host Reference Voltage:

Reference voltage input for the Data, Address, and Common clock

signals of the Host AGTL+ interface.

HXRCOMP I/O

A

Host X RCOMP:

Used to calibrate the Host AGTL+ I/O buffers.

This signal is powered by the Host Interface termination rail (VCCP).

HXSCOMP I/O

A

Host X SCOMP:

Slew Rate Compensation for the Host Interface

HXSWING I

A

Host X Voltage Swing:

These signals provide reference voltages used by the HXRCOMP

circuits.

HYRCOMP

I/O

A

Host Y RCOMP

:

Used to calibrate the Host AGTL+ I/O buffers.

HYSCOMP I/O

A

Host Y SCOMP:

Slew Rate Compensation for the Host Interface

HYSWING I

A

Host Y Voltage Swing:

These signals provide reference voltages used by the HYRCOMP

circuitry.

DMI

Signal Name Type Description

DMI_RXP[1:0]

DMI_RXN[1:0]

I

PCIE

DMI input from ICH6-M:

Direct Media Interface receive differential pair

DMI_TXP[1:0]

DMI_TXN[1:0]

O

PCIE

DMI output to ICH6-M:

Direct Media Interface transmit differential pair

DMI x2 is supported for Intel 915GMS chipset

MiTac Secret

Confidential Document