94

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

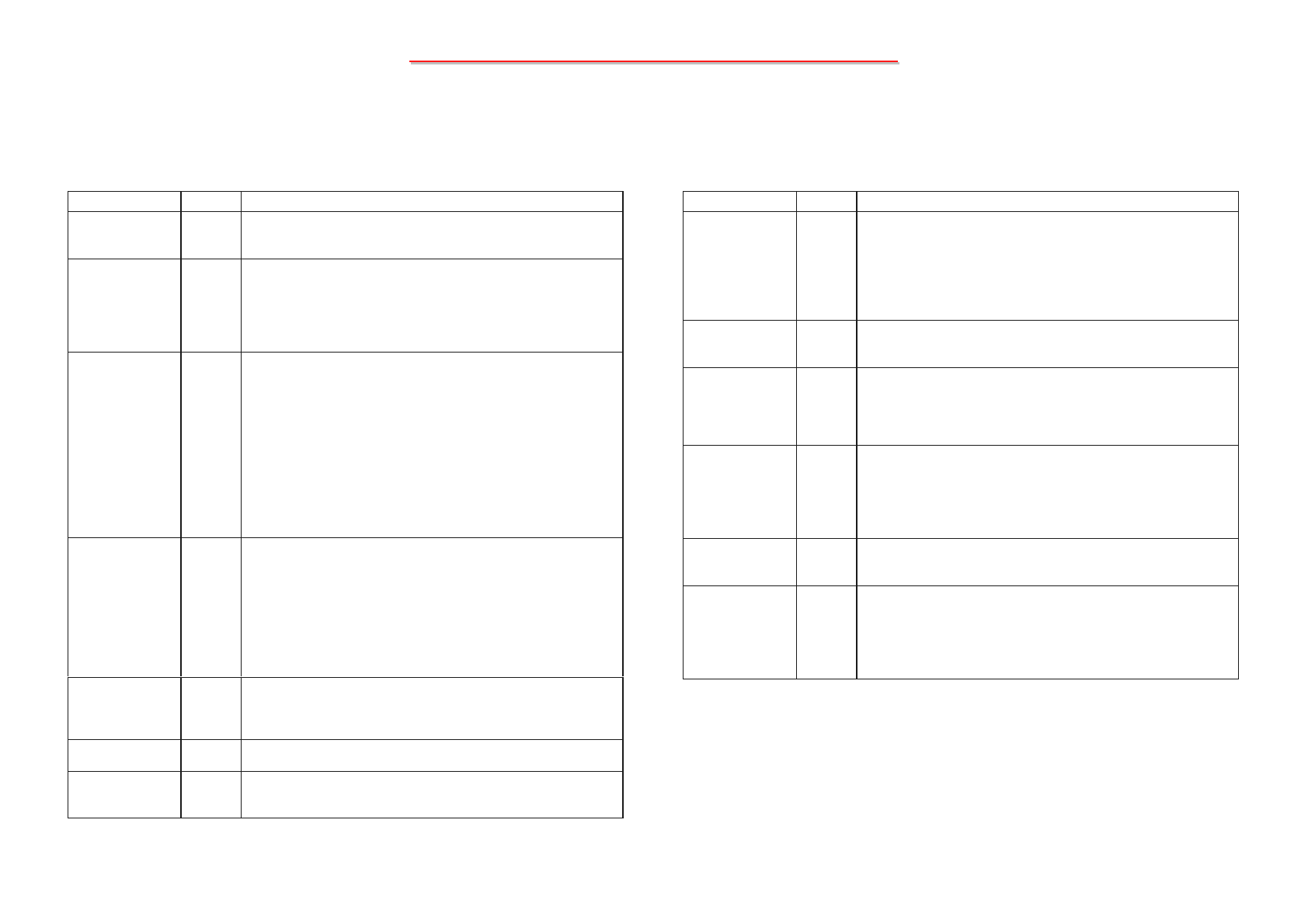

5.2 Intel ICH6-M South Bridge(7)

Processor Interface Signals

Name Type Description

A20M#

O Mask A20: A20M# will go active based on either setting the

appropriate bit in the Port 92h register, or based on the A20GATE

input being active.

CPUSLP#

O Processor Sleep: This signal puts the processor into a state that saves

substantial power compared to Stop-Grant state. However, during that

time, no snoops occur.

The Intel® ICH6 can optionally assert the CPUSLP# signal when

going to the S1 state, and will always assert it when going to C3 or

C4.

FERR#

I Numeric Coprocessor Error: This signal is tied to the coprocessor

error signal on the processor. FERR# is only used if the ICH6

coprocessor error reporting function is enabled in the OIC.CEN

register (Chipset ConfigurationRegisters:Offset 31FFh: bit 1). If

FERR# is asserted, the ICH6 generates an internal IRQ13 to its

interrupt controller unit. It is also used to gate the IGNNE# signal to

ensure that IGNNE# is not asserted to the processor unless FERR# is

active. FERR# requires an external weak pull-up to ensure a high

level when the coprocessor error function is disabled.

NOTE: FERR# can be used in some states for notification by the

processor of pending interrupt events. This functionality is

independent of the OIC register bit setting.

IGNNE#

O Ignore Numeric Error: This signal is connected to the ignore error

pin on the processor. IGNNE# is only used if the ICH6 coprocessor

error reporting function is enabled in the OIC.CEN register (Chipset

Configuration Registers:Offset 31FFh: bit 1). If FERR# is active,

indicating a coprocessor error, a write to the Coprocessor Error

register (I/O register F0h) causes the IGNNE# to be asserted.

IGNNE# remains asserted until FERR# is negated. If FERR# is not

asserted when the Coprocessor Error register is written, the IGNNE#

signal is not asserted.

INIT#

O Initialization: INIT# is asserted by the ICH6 for 16 PCI clocks to

reset the processor.

ICH6 can be configured to support processor Built In Self Test

(BIST).

INIT3_3V#

O

Initialization 3.3 V:

This is the identical 3.3 V copy of INIT#

intended for Firmware Hub.

INTR

O Processor Interrupt: INTR is asserted by the ICH6 to signal the

processor that an interrupt request is pending and needs to be

serviced. It is an asynchronous output and normally driven low.

Processor Interface Signals (Continued)

Name Type Description

NMI

O Non-Maskable Interrupt: NMI is used to force a non-Maskable

interrupt to the processor. The ICH6 can generate an NMI when

either SERR# is asserted or IOCHK# goes active via the SERIRQ#

stream. The processor detects an NMI when it detects a rising edge on

NMI. NMI is reset by setting the corresponding NMI source

enable/disable bit in the NMI Status and Control register (I/O

Register 61h).

SMI#

O System Management Interrupt: SMI# is an active low output

synchronous to PCICLK. It is asserted by the ICH6 in response to one

of many enabled hardware or software events.

STPCLK#

O Stop Clock Request: STPCLK# is an active low output synchronous

to PCICLK. It is asserted by the ICH6 in response to one of many

hardware or software events.

When the processor samples STPCLK# asserted, it responds by

stopping its internal clock.

RCIN#

I Keyboard Controller Reset CPU: The keyboard controller can

generate INIT# to the processor. This saves the external OR gate with

the ICH6’s other sources of INIT#. When the ICH6 detects the

assertion of this signal, INIT# is generated for 16 PCI clocks.

NOTE: The ICH6 will ignore RCIN# assertion during transitions to

the S1, S3, S4, and S5 states.

A20GATE

I A20 Gate: A20GATE is from the keyboard controller. The signal

acts as an alternative method to force the A20M# signal active. It

saves the external OR gate needed with various other chipsets.

CPUPWRGD /

GPO[49]

OD

O

Processor Power Good: This signal should be connected to the

processor’s PWRGOOD input to indicate when the processor power

is valid. This is an open- drain output signal (external pull-up resistor

required) that represents a logical AND of the ICH6’s PWROK and

VRMPWRGD signals.

This signal may optionally be configured as a GPO.

MiTac Secret

Confidential Document