96

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

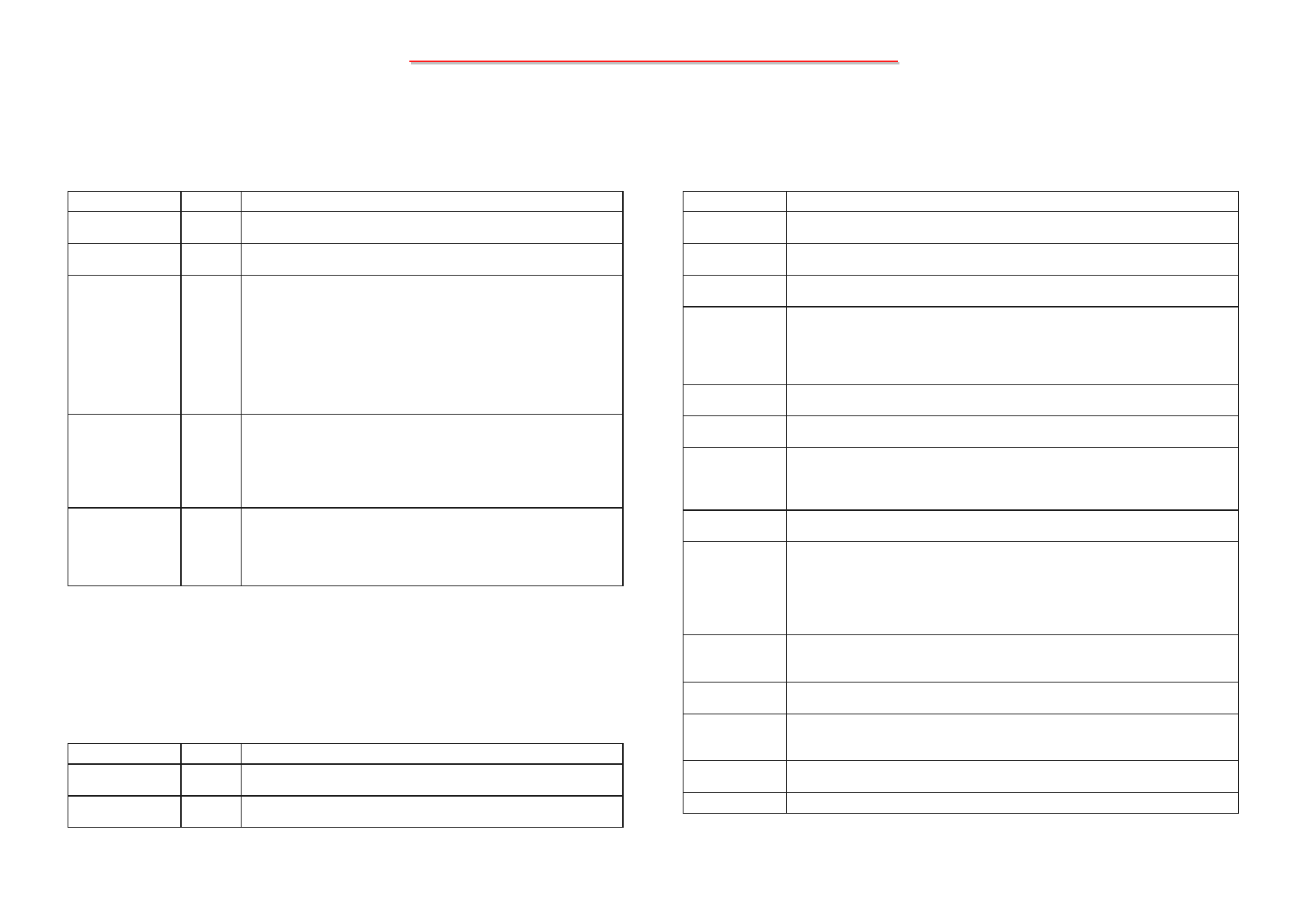

5.2 Intel ICH6-M South Bridge(9)

Power and Ground Signals

Name Description

Vcc3_3

3.3 V supply for core well I/O buffers (22 pins). This power may be shut off in S3,

S4, S5 or G3 states.

Vcc1_5_A

1.5 V supply for core well logic, group A (52 pins). This power may be shut off in

S3, S4, S5 or G3 states.

Vcc1_5_B

1.5 V supply for core well logic, group B (45 pins). This power may be shut off in

S3, S4, S5 or G3 states.

Vcc2_5

2.5V supply for internal logic (2 pins). This power may be shut off in S3, S4, S5 or

G3 states.

NOTE: This voltage may be generated internally (see Section 2.22.1 for strapping

option). If generated internally, these pins should not be connected to an external

supply.

V5REF

Reference for 5 V tolerance on core well inputs (2 pins). This power may be shut

off in S3, S4, S5 or G3 states.

VccSus3_3

3.3 V supply for resume well I/O buffers (20 pins). This power is not expected to

be shut off unless the system is unplugged.

VccSus1_5

1.5 V supply for resume well logic (3 pin). This power is not expected to be shut

off unless the system is unplugged.

This voltage may be generated internally (see Section 2.22.1 for strapping option).

If generated internally, these pins should not be connected to an external supply.

V5REF_Sus

Reference for 5 V tolerance on resume well inputs (1 pin). This power is not

expected to be shut off unless the system is unplugged.

VccRTC

3.3 V (can drop to 2.0 V min. in G3 state) supply for the RTC well (1 pin). This

power is not expected to be shut off unless the RTC battery is removed or

completely drained.

NOTE: Implementations should not attempt to clear CMOS by using a jumper to

pull VccRTC low. Clearing CMOS in an ICH6-based platform can be done by

using a jumper on RTCRST# or GPI.

VccUSBPLL

1.5 V supply for core well logic (1 pin). This signal is used for the USB PLL. This

power may be shut off in S3, S4, S5 or G3 states. This signal must be powered

even if USB not used.

VccDMIPLL

1.5 V supply for core well logic (1 pins). This signal is used for the DMI PLL. This

power may be shut off in S3, S4, S5 or G3 states.

VccSATAPLL

1.5 V supply for core well logic (1 pins). This signal is used for the SATA PLL.

This power may be shut off in S3, S4, S5 or G3 states. This signal must be

powered even if SATA not used.

V_CPU_IO

Powered by the same supply as the processor I/O voltage (3 pins). This supply is

used to drive the processor interface signals listed in Table 2-13.

Vss

Grounds (172 pins).

AC ’97/Intel ® High Definition Audio Link Signals

NOTES:

1. Some signals have integrated pull-ups or pull-downs. Consult table in Section 3.1 for

details.

2. Intel High Definition Audio mode is selected through D30:F1:40h, bit 0: AZ/AC97#. This

bit selects the mode of the shared Intel High Definition Audio/AC ‘97 signals. When set to 0

AC ’97 mode is selected. When set to 1 Intel High Definition Audio mode is selected. The bit

defaults to 0 (AC ‘97 mode).

Name Type Description

ACZ_RST#

O AC ’97/Intel ® High Definition Audio Reset: Master hardware reset

to external codec(s).

ACZ_SYNC

O AC ’97/Intel High Definition Audio Sync: 48 kHz fixed rate sample

sync to the codec(s). Also used to encode the stream number.

ACZ_BIT_CLK

I/O AC ’97 Bit Clock Input: 12.288 MHz serial data clock generated by

the external codec(s). This signal has an integrated pull-down resistor

(see Note below).

Intel High Definition Audio Bit Clock Output: 24.000 MHz serial

data clock generated by the Intel® High Definition Audio controller

(the Intel ICH6). Thissignal has an integrated pull-down resistor so

that ACZ_BIT_CLK does not float when an

Intel High Definition Audio codec (or no codec) is connected but the

signals are temporarily configured as AC ’97.

ACZ_SDOUT

O AC ’97/Intel High Definition Audio Serial Data Out: Serial TDM

data output to the codec(s). This serial output is double-pumped for a

bit rate of 48 Mb/s for Intel High Definition Audio.

NOTE: ACZ_SDOUT is sampled at the rising edge of PWROK as a

functional strap. See Section 2.22.1 for more details. There is a weak

integrated pull-down resistor on the ACZ_SDOUT pin.

ACZ_SDIN[2:0]

I AC ’97/Intel High Definition Audio Serial Data In [2:0]: Serial

TDM data inputs from the three codecs. The serial input is

single-pumped for a bit rate of 24 Mb/s for Intel High Definition

Audio. These signals have integrated pull-down resistors, which are

always enabled.

Firmware Hub Interface Signals

Name Type Description

FWH[3:0] /

LAD[3:0]

I/O Firmware Hub Signals. These signals are multiplexed with the LPC

address signals.

FWH[4]

/

LFRAME#

O

Firmware Hub Signals.

This signal is multiplexed with the LPC

LFRAME# signal.

MiTac Secret

Confidential Document