91

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

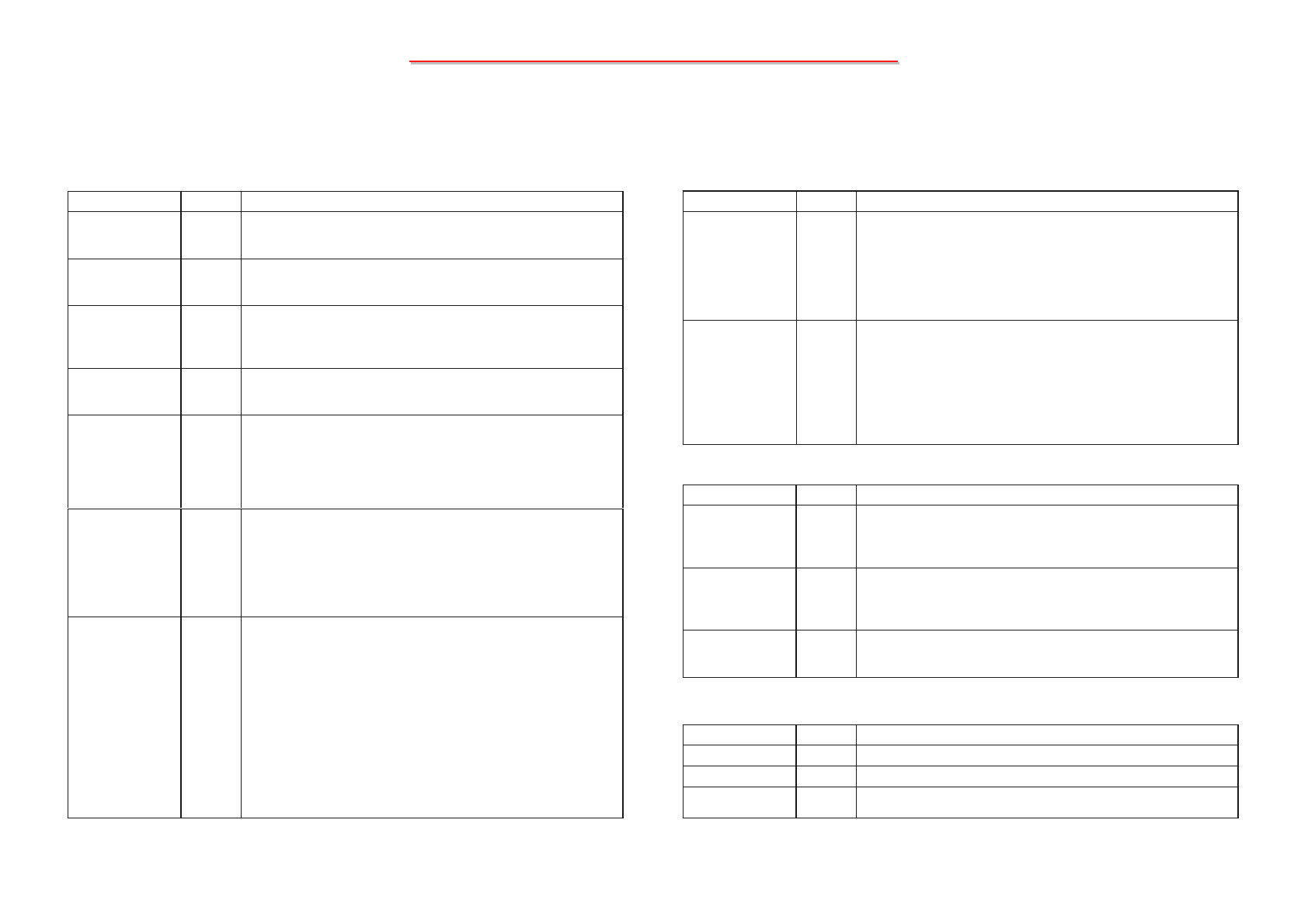

5.2 Intel ICH6-M South Bridge(4)

IDE Interface Signals

Name Type Description

DCS1#

O IDE Device Chip Selects for 100 Range: For ATA command

register block. This output signal is connected to the corresponding

signal on the IDE connector.

DCS3#

O IDE Device Chip Select for 300 Range: For ATA control register

block. This output signal is connected to the corresponding signal on

the IDE connector.

DA[2:0]

O IDE Device Address: These output signals are connected to the

corresponding signals on the IDE connector. They are used to indicate

which byte in either the ATA command block or control block is

being addressed.

DD[15:0]

I/O

IDE Device Data:

These signals directly drive the corresponding

signals on the IDE connector. There is a weak internal pull-down

resistor on DD7.

DDREQ

I IDE Device DMA Request: This input signal is directly driven from

the DRQ signal on the IDE connector. It is asserted by the IDE device

to request a data transfer, and used in conjunction with the PCI bus

master IDE function and are not associated with any AT compatible

DMA channel. There is a weak internal pull-down resistor on this

signal.

DDACK#

O IDE Device DMA Acknowledge: This signal directly drives the

DAK# signal on the IDE connector. DDACK# is asserted by the Intel

ICH6 to indicate to IDE DMA slave devices that a given data transfer

cycle (assertion of DIOR# or DIOW#) is a DMA data transfer cycle.

This signal is used in conjunction with the PCI bus master IDE

function and are not associated with any AT-compatible DMA

channel.

DIOR# / (DWSTB

/ RDMARDY#)

O

DIOR# /

Disk I/O Read (PIO and Non-Ultra DMA): This is the command to

the IDE device that it may drive data onto the DD lines. Data is

latched by the ICH6 on the de-assertion edge of DIOR#. The IDE

device is selected either by the ATA register file

chip selects (DCS1# or DCS3#) and the DA lines, or the IDE DMA

acknowledge (DDAK#)

Disk Write Strobe (Ultra DMA Writes to Disk): This is the data write

strobe for writes to disk. When writing to disk, ICH6 drives valid data

on rising and falling edges of DWSTB.

Disk DMA Ready (Ultra DMA Reads from Disk): This is the DMA

ready for reads from disk. When reading from disk, ICH6 de-asserts

RDMARDY# to pause burst data transfers.

IDE Interface Signals (Continued)

Name Type Description

DIOW# / (DSTOP) O Disk I/O Write (PIO and Non-Ultra DMA): This is the command to

the IDE device that it may latch data from the DD lines. Data is

latched by the IDE device on the de-assertion edge of DIOW#. The

IDE device is selected either by the ATA register file chip selects

(DCS1# or DCS3#) and the DA lines, or the IDE DMA acknowledge

(DDAK#).

Disk Stop (Ultra DMA): ICH6 asserts this signal to terminate a burst.

IORDY / (DRSTB

/ WDMARDY#)

I I/O Channel Ready (PIO): This signal will keep the strobe active

(DIOR# on reads, DIOW# on writes) longer than the minimum width.

It adds wait-states to PIO transfers.

Disk Read Strobe (Ultra DMA Reads from Disk): When reading from

disk, ICH6 latches data on rising and falling edges of this signal from

the disk.

Disk DMA Ready (Ultra DMA Writes to Disk): When writing to

disk, this is de-asserted by the disk to pause burst data transfers.

System Management Interface Signals

Name Type Description

INTRUDER#

I Intruder Detect: This signal can be set to disable system if box

detected open.

This signal’s status is readable, so it can be used like a GPI if the

Intruder Detection is not needed.

SMLINK[1:0]

OD I/O System Management Link: SMBus link to optional external system

management ASIC or LAN controller. External pull-ups are required.

Note that SMLINK0 corresponds to an SMBus Clock signal, and

SMLINK1 corresponds to an SMBus Data signal.

LINKALERT#

OD I/O SMLink Alert: Output of the integrated LAN and input to either the

integrated ASF or an external management controller in order for the

LAN’s SMLINK slave to be serviced.

SM Bus Interface Signals

Name Type Description

SMBDATA

OD I/O SMBus Data: External pull-up resistor is required.

SMBCLK

OD I/O SMBus Clock: External pull-up resistor is required.

SMBALERT#/

GPI[11]

I SMBus Alert: This signal is used to wake the system or generate

SMI#. If not used for SMBALERT#, it can be used as a GPI.

MiTac Secret

Confidential Document