93

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

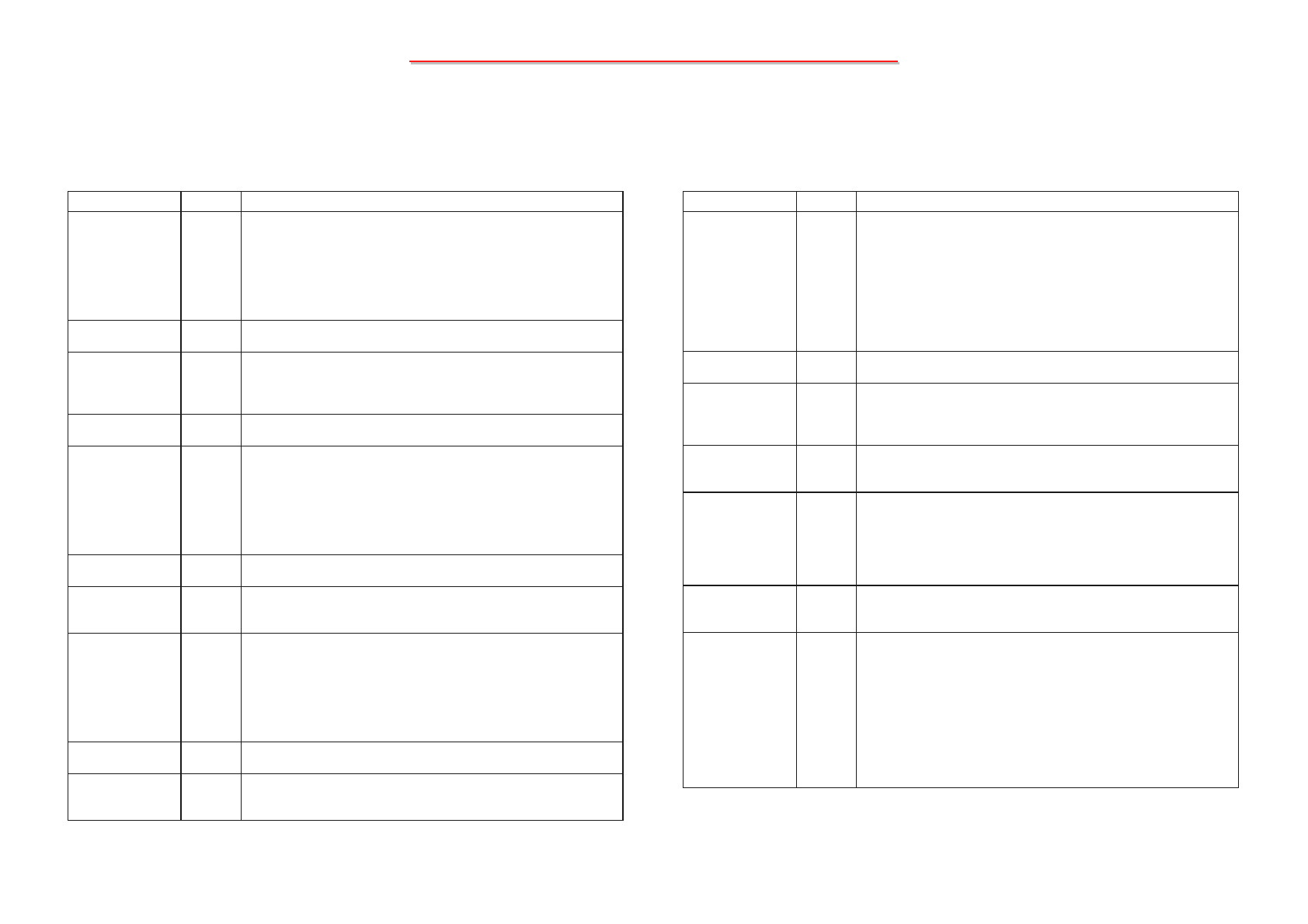

5.2 Intel ICH6-M South Bridge(6)

Power Management Interface Signals

Name Type Description

PWRBTN#

I Power Button: The Power Button will cause SMI# or SCI to indicate

a system request to go to a sleep state. If the system is already in a

sleep state, this signal will cause a wake event. If PWRBTN# is

pressed for more than 4 seconds, this will cause an unconditional

transition (power button override) to the S5 state. Override will occur

even if the system is in the S1-S4 states. This signal has an internal

pull-up resistor and has an internal 16 ms de-bounce on the input.

RI#

I Ring Indicate: This signal is an input from a modem. It can be

enabled as a wake event, and this is preserved across power failures.

SYS_RESET#

I System Reset: This pin forces an internal reset after being debounced.

The ICH6 will reset immediately if the SMBus is idle; otherwise, it

will wait up to 25 ms ± 2 ms for the SMBus to idle before forcing a

reset on the system.

RSMRST#

I Resume Well Reset: This signal is used for resetting the resume

power plane logic.

LAN_RST#

I LAN Reset: When asserted, the internal LAN controller will be put

into reset. This signal must be asserted for at least 10 ms after the

resume well power (VccSus3_3 and VccSus1_5) is valid. When

de-asserted, this signal is an indication that the resume well power is

stable.

NOTE: LAN_RST# must de-assert at some point to complete ICH6

power up sequencing.

WAKE#

I PCI Express* Wake Event: Sideband wake signal on PCI Express

asserted by components requesting wakeup.

MCH_SYNC#

I MCH SYNC: This input is internally ANDed with the PWROK

input.

Connected to the ICH_SYNC# output of (G)MCH.

SUS_STAT# /

LPCPD#

O Suspend Status: This signal is asserted by the ICH6 to indicate that

the system will be entering a low power state soon. This can be

monitored by devices with memory that need to switch from normal

refresh to suspend refresh mode. It can also be used by other

peripherals as an indication that they should isolate their outputs that

may be going to powered-off planes. This signal is called LPCPD# on

the LPC I/F.

SUSCLK

O

Suspend Clock:

This clock is an output of the RTC generator circuit

to use by other chips for refresh clock.

VRMPWRGD

I VRM Power Good: This should be connected to be the processor’s

VRM Power Good signifying the VRM is stable. This signal is

internally ANDed with the PWROK input.

Power Management Interface Signals (Continued)

Name Type Description

PLTRST#

O Platform Reset: The ICH6 asserts PLTRST# to reset devices on the

platform (e.g., SIO, FWH, LAN, (G)MCH, IDE, TPM, etc.). The

ICH6 asserts PLTRST# during power-up and when S/W initiates a

hard reset sequence through the Reset Control register (I/O Register

CF9h). The ICH6 drives PLTRST# inactive a minimum of 1 ms after

both PWROK and VRMPWRGD are driven high. The ICH6 drives

PLTRST# active a minimum of 1 ms when initiated through the Reset

Control register (I/O Register CF9h).

NOTE: PLTRST# is in the VccSus3_3 well.

THRM#

I Thermal Alarm: This is an active low signal generated by external

hardware to generate an SMI# or SCI.

THRMTRIP#

I Thermal Trip: When low, this signal indicates that a thermal trip

from the processor occurred, and the ICH6 will immediately

transition to a S5 state. The ICH6 will not wait for the processor stop

grant cycle since the processor has overheated.

SLP_S3#

O S3 Sleep Control: SLP_S3# is for power plane control. This signal

shuts off power to all non-critical systems when in S3 (Suspend To

RAM), S4 (Suspend to Disk), or S5 (Soft Off) states.

SLP_S4#

O S4 Sleep Control: SLP_S4# is for power plane control. This signal

shuts power to all non-critical systems when in the S4 (Suspend to

Disk) or S5 (Soft Off) state.

NOTE:

This pin must be used to control the DRAM power in order

to use the ICH6’s DRAM power-cycling feature. Refer to Chapter

5.14.10.2 for details.

SLP_S5#

O S5 Sleep Control: SLP_S5# is for

p

ower plane control. This signal is

used to shut power off to all non-critical systems when in the S5 (Soft

Off) states.

PWROK

I Power OK: When asserted, PWROK is an indication to the ICH6

that core power has been stable for at least 99 ms and PCICLK has

been stable for at least 1 mS. An exception to this rule is if the system

is in S3 HOT , in which PWROK may or may notstay asserted even

though PCICLK may be inactive. PWROK can be driven

asynchronously. When PWROK is negated, the ICH6 asserts

PLTRST#.

NOTE: PWROK must de-assert for a minimum of three RTC clock

periods in order for the ICH6 to fully reset the power and properly

generate the PLTRST# output

MiTac Secret

Confidential Document