81

80

80

50QMA

50QMA

N/B Maintenance

N/B Maintenance

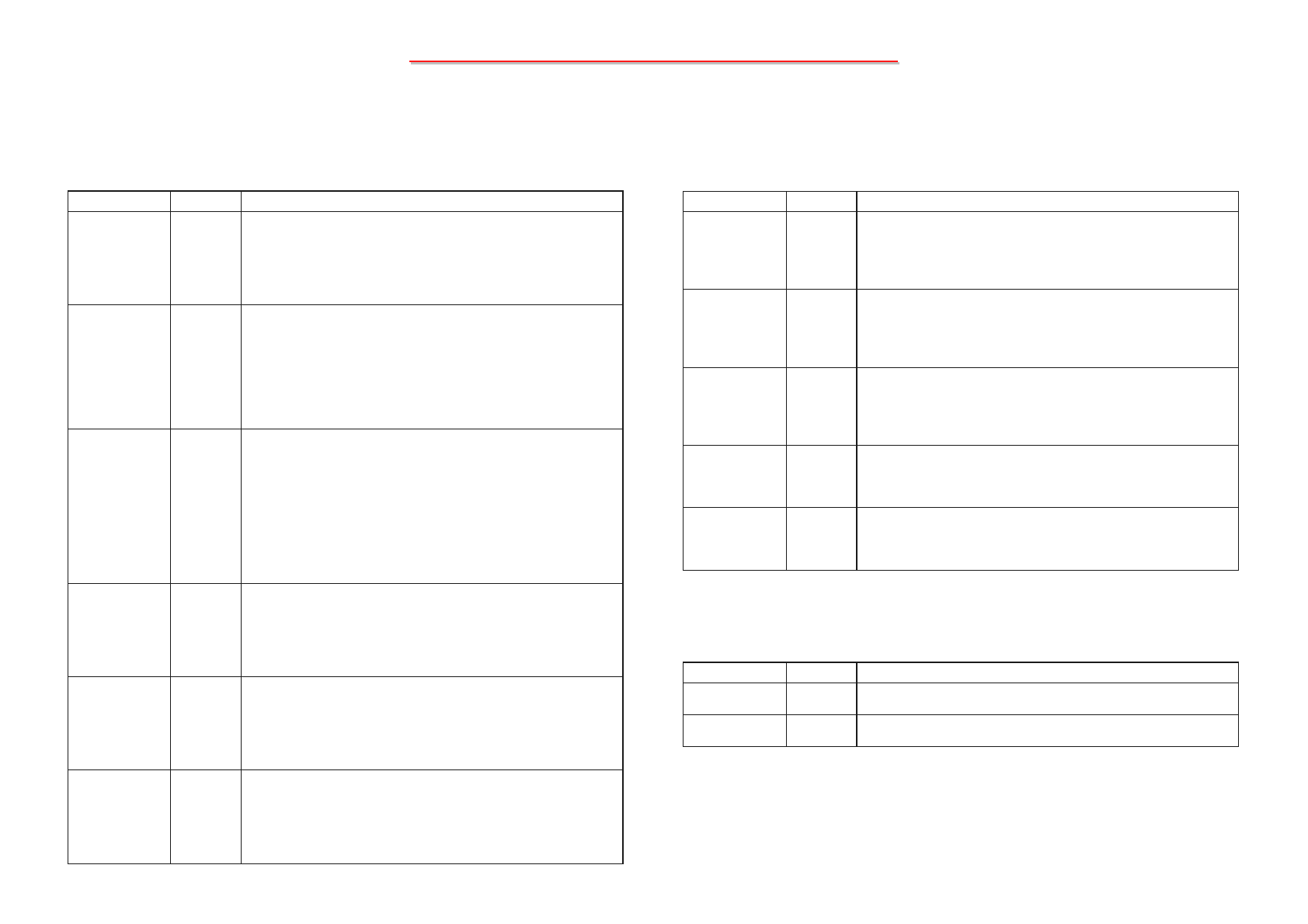

5.1 Intel 915PM North Bridge(4)

DDR / DDR2 SDRAM Channel B Interface

Signal Name Type Description

SB_DQ[63:0] I/O

SSTL1.8/2

2x

Data Lines:

DDR / DDR2 Channel B data signal interface to the SDRAM data

bus.

Single Channel mode: No connect.

Dual channel mode: Route to SO-DIMM B

NOTE: Signals do not exist in Intel 915GMS.

SB_DM[7:0] O

SSTL1.8/2

2x

Data Mask:

When activated during writes, the corresponding data groups in the

SDRAM are masked. There is one SB_DM[7:0] for every data byte

lane. These signals are used to mask individual bytes of data in the

case of a partial write, and to interrupt burst writes.

Single Channel mode: No connect.

Dual channel mode: Route to SO-DIMM B

NOT

E: Signals do not exist in Intel 915GMS.

SB_DQS[7:0] I/O

SSTL1.8/2

2x

Data Strobes:

DDR: The rising and falling edges of SB_DQS[7:0] are used for

capturing data during read and write transactions.

DDR2: SB_DQS[7:0] and its complement signal group make up a

differential strobe pair. The data is captured at the crossing point of

SB_DQS[7:0] and its SB_DQS[7:0]# during read and write

transactions.

Single Channel mode: No connect.

Dual channel mode: Route to SO-DIMM B

NOTE: Signals do not exist in Intel 915GMS.

SB_DQS[7:0]# I/O

SSTL1.8

2x

Data Strobe Complements (DDR2 only):

DDR1: No Connect. These signals are not used for DDR devices

DDR2 : These are the complementary DDR2 strobe signals.

Single Channel mode: No connect.

Dual channel mode: Route to SO-DIMM B

NOT

E: Signals do not exist in Intel 915GMS.

SB_MA[13:0] O

SSTL1.8/2

Memory Address:

These signals are used to provide the multiplexed row and column

address to the SDRAM.

Single channel mode: Route to SO-DIMM 1

Dual channel mode: Route to SO-DIMM B

NOTE: SB_MA13 is for support of 1 Gb devices.

SB_BS[2:0] O

SSTL1.8/2

Bank Select:

These signals define which banks are selected within each

SDRAM rank.

Single channel mode: Route to SO-DIMM 1

Dual channel mode: Route to SO-DIMM B

NOTE: SB_BS2 is for DDR2 support only.

DDR / DDR2 SDRAM Channel B Interface (Continued)

Signal Name Type Description

SB_RAS# O

SSTL1.8/2

RAS Control signal:

Used with SB_CAS# and SB_WE# (along with SM_CS#) to define

the SDRAM commands.

Single channel mode: Route to SO-DIMM 1

Dual channel mode: Route to SO-DIMM B

SB_CAS# O

SSTL1.8/2

CAS Control signal:

Used with SB_RAS# and SB_WE# (along with SM_CS#) to define

the SDRAM commands.

Single channel mode: Route to SO-DIMM 1

Dual channel mode: Route to SO-DIMM B

SB_WE# O

SSTL1.8/2

Write Enable Control signal:

Used with SB_RAS# and SB_CAS# (along with SM_CS#) to define

the SDRAM commands.

Single channel mode: Route to SO-DIMM 1

Dual channel mode: Route to SO-DIMM B

SB_RCVENIN# I

SSTL1.8/2

Clock Input:

Used to emulate source-synch clocking for reads.

Leave as No Connect.

NOTE: Signals do not exist in Intel 915GMS.

SB_RCVENOUT

#

O

SSTL1.8/2

Clock Output:

Used to emulate source-synch clocking for reads.

Leave as No Connect.

NOTE: Signals do not exist in Intel 915GMS.

DMI

Signal Name Type Description

DMI_RXP[3:0]

DMI_RXN[3:0]

I

PCIE

DMI input from ICH6-M:

Direct Media Interface receive differential pair

DMI_TXP[3:0]

DMI_TXN[3:0]

O

PCIE

DMI output to ICH6-M:

Direct Media Interface transmit differential pair

DMI x2 or x4 is supported for Intel 915GM, Intel 915PM and Intel 910GML chipsets.

MiTac Secret

Confidential Document