M30850T2-EPB User’s Manual 3. Usage (How to Use the Emulator Debugger)

REJ10J1005-0200 Rev.2.00 April 1, 2007

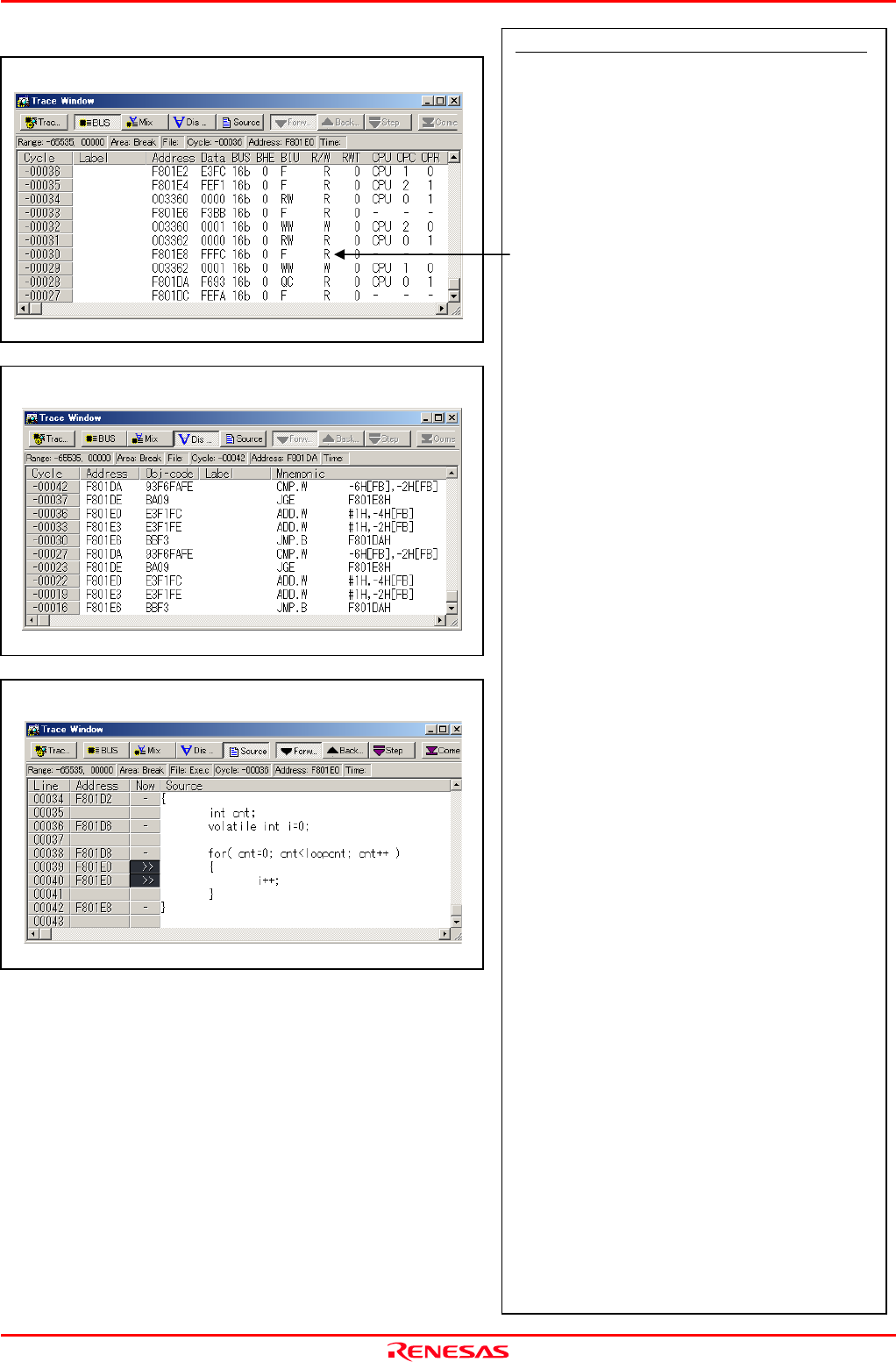

Explanation of the trace window (bus display)

2. Trace window (bus display)

Bus display

The following explains the displayed contents, from left to

right.

- Address

Shows the status of the address bus.

- Data

Shows the status of the data bus.

- BUS

Shows the width of the external data bus. In the present

emulator, only “16b” for 16 bits wide bus is displayed.

- BHE*

Shows the status (0 or 1) of the BHE (Byte High Enable)

signal. If this signal = 0, the odd-address data is valid.

- BIU

Shows the status between the BIU (Bus Interface Unit) and

memory or I/O.

Disassemble display

Symbol Status

- No change

WAIT Executing the wait instruction

RBML Read (bytes) ML on

F Fetch

QC Discontinuous fetch

RWML Read (words) ML on

INT Interrupt acknowledge cycle

RB Read (bytes)

WB Write (bytes)

DRB Read (bytes) by DMA

DWB Write (bytes) by DMA

RW Read (words)

WW Write (words)

Source display

DRW Read (words) by DMA

DWW Write (words) by DMA

- R/W

Shows the status of the data bus.

Displayed as “R” for Read, “W” for Write, and “–” for no

access.

- RWT

This is the signal to indicate a valid bus cycle. When valid,

RWT = 0. The Address, Data, and the BIU signals are

effective when this signal is 0.

- CPU

Shows the status between the CPU and BIU (Bus Interface

Unit).

- OPC

Shows the op-code size in the read data.

- OPR

Shows the code size except op-code.

- QN

Shows the byte count stored in the instruction queue buffer.

The display range is 0 to 8.

- B-T

Shows the level of the trigger signal for break event

(EXTIN7 pin of external trace signal input cable, purple).

- Q-T

Shows the level of the trigger signal for trace event

(EXTIN6 pin of external trace signal input cable, blue).

- 76543210

Shows the level of external trace signal input cable EXTIN0

to EXTIN7.

- h” m’ s: ms. us

Shows the elapsed time after starting the user program.

Page 68 of 98