Status and Events

Option 01 VXI Interface Module User Manual

4–3

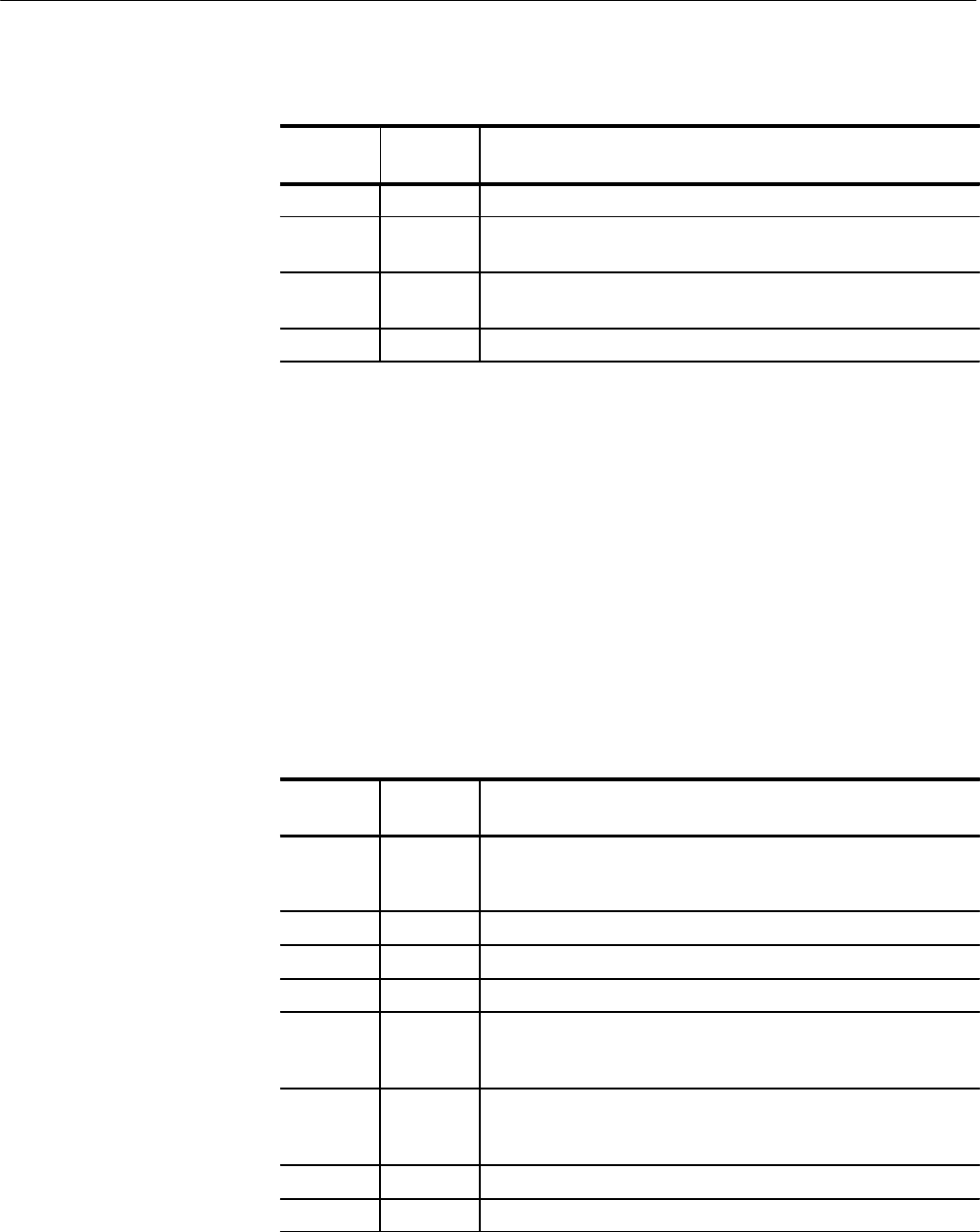

Table 4–2: The Service Request Enable Register (Cont.)

Bit Function

Decimal

Value

3 8 Not used

4 16 Message Available Bit indicates that a service request will be

generated when a message is placed in the Output queue.

5 32 Event Status Bit indicates that events summarized in bit 5 of the

Status Byte register will generate a service request.

6–7 – Not used

If, for example, the *SRE? query returns a value of 48, bits 4 and 5 are set in the

Service Request Enable register. Any event that causes the Message Available bit

(bit 4) or Event Status bit (bit 5) to be set in the Status Byte register now

generates an interrupt. If you want an interrupt to be generated only when the

Event Status bit (bit 5) is set, use the *SRE 32 command.

The Standard Event Status register, shown in Table 4–3, records many types of

events that can occur in the Option 01. Use the *ESR? query to read the contents

of this register. The response is the sum of the decimal values for all bits set.

Reading this register clears all bits so the register can accumulate information

about new events.

Table 4–3: The Standard Event Status Register

Bit

Decimal

Value

Function

0 1 Operation Complete shows that the operation is complete. This bit

is set when all pending operations complete following a *OPC

command.

1 – Not used

2 4 Query Error shows that data in the Output queue was lost.

3 8 Not used

4 16 Execution Error shows that an error occurred while the Option 01

was executing a command or query. Table 4–6 on page 4–7 lists

the execution error messages.

5 32 Command Error shows that an error occurred while the Option 01

was parsing a command or query. Table 4–5 on page 4–6 lists the

command error messages.

6 – Not used

7 128 Power On shows that the Option 01 was powered on.

Standard Event Status

Register