TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL 1992–REVISED MARCH 1993

POST OFFICE BOX 1443 • HOUSTON, TEXAS

77251–1443

46

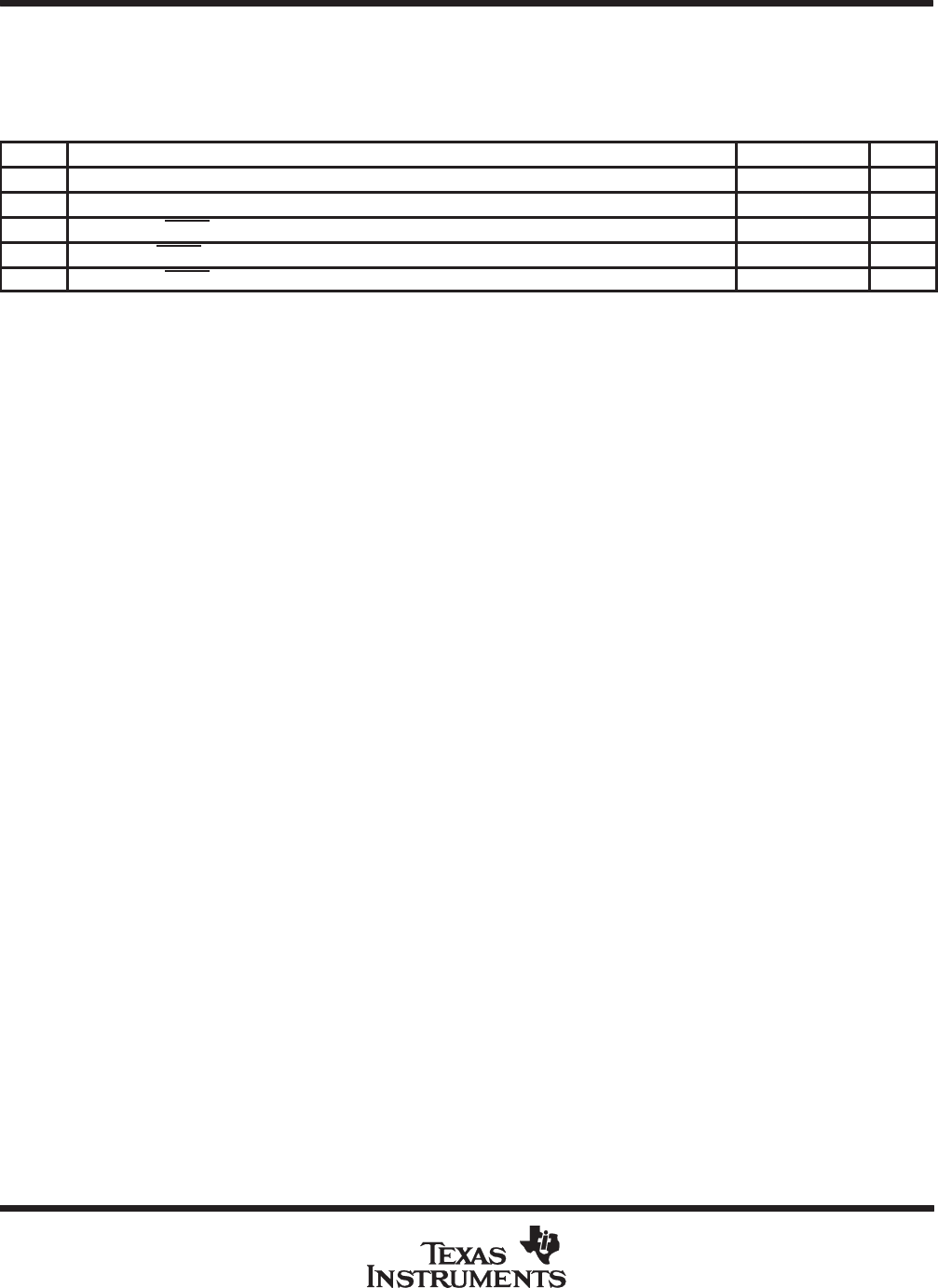

PARAMETER MEASUREMENT INFORMATION

memory bus timing: TMS380C26 resumes control of bus

t

M

is the cycle time of one-eighth of a local memory cycle (31.25 ns minimum)

NO. PARAMETER MIN MAX UNIT

79 Hold time of MIF output high impedance after MBCKL1 rising edge, bus resume t

M

– 13 ns

80 Delay time from MBCLK1 high to MIF output vallid, bus resume t

M

+ 9 ns

91 Setup time of MBRQ valid before MBCLK1 falling edge, bus resume 24 ns

82 Hold time of MBRQ valid after MBCLK1 low, bus resume 0 ns

83 Setup time of MBGR high before MBCLK1 rising edge, bus resume 29 ns