TMS380C26

NETWORK COMMPROCESSOR

SPWS010A–APRIL 1992–REVISED MARCH 1993

POST OFFICE BOX 1443 • HOUSTON, TEXAS

77251–1443

74

PARAMETER MEASUREMENT INFORMATION

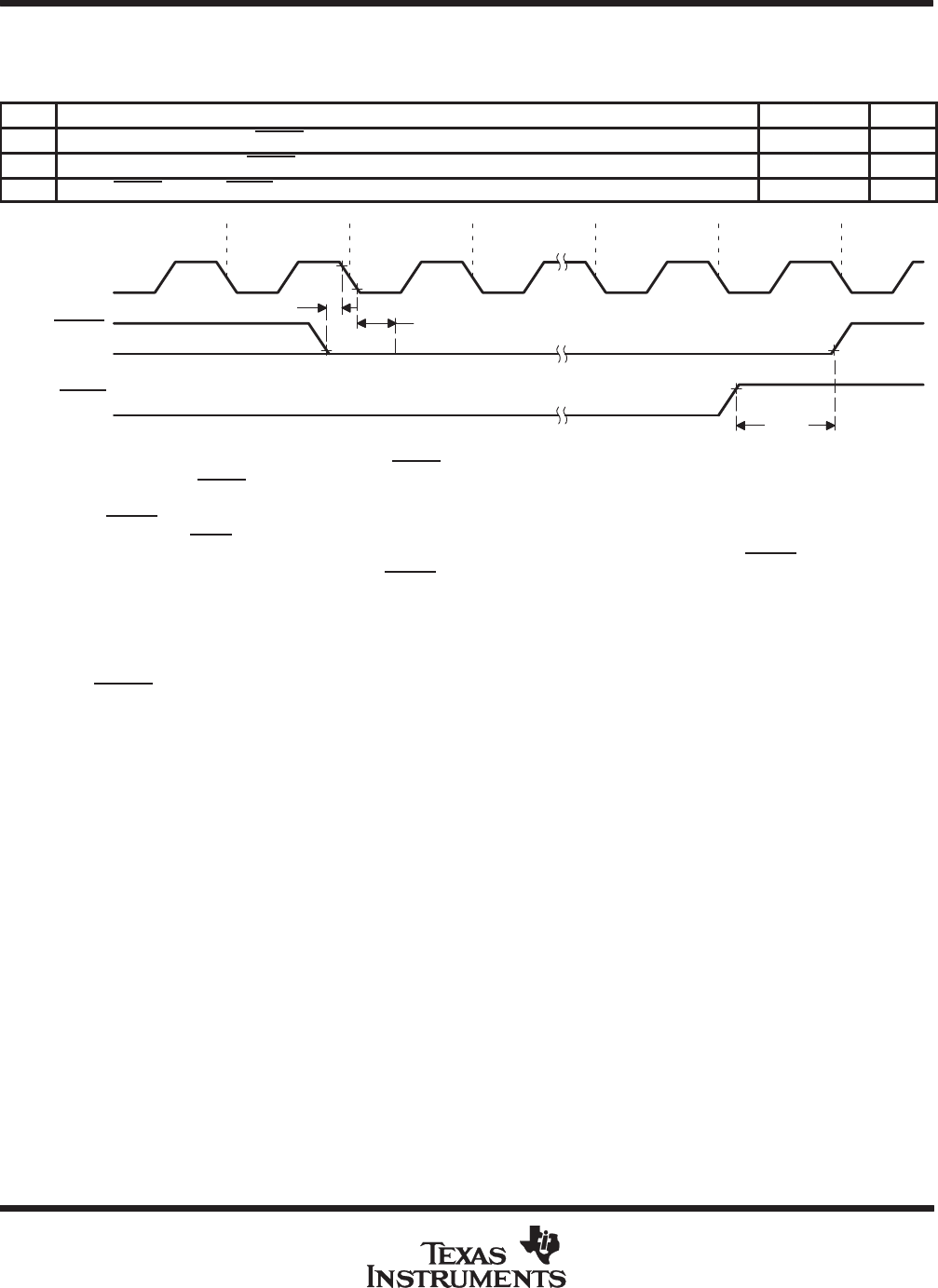

80x8x mode bus release timing

NO. PARAMETER MIN MAX UNIT

208a Setup of asynchronous input SBRLS low before SBCLK no longer high to guarantee recognition 15 ns

208b Hold of asynchronous input SBRLS low after SBCLK low to guarantee recognition 15 ns

208c Hold of SBRLS low after SOWN high 0 ns

SOWN

SBRLS

(see Note A)

SBCLK

208b

208a

T(W or 2) T3 T4 T1 T2

208c

NOTES: A. The System Interface ignores the assertion of SBRLS

if it does not own the system bus. If it does own the bus, then when it detects

the assertion of SBRLS

, it will complete any internally started DMA cycle and relinquish control of the bus. If no DMA transfer has

internally started, then the System Interface will release the bus before starting another.

B. If SBERR

is asserted when the System Interface controls the system bus, then the current bus transfer is completed, regardless

of the value of SRDY

. If the BERETRY register is non-zero, the cycle will be retried. If the BERETRY register is zero, the System

Interface will then release control of the system bus. The System Interface ignores the assertion of SBERR

if it is not performing

a DMA bus cycle on the system bus. When SBERR

is properly asserted and BERETRY is zero, however, the System Interface

releases the bus upon completion of the current bus transfer and halts all further DMA on the system side. The error is synchronized

to the local bus and DMA stops on the local sides. The value of the SDMAADR, SDMADDRX, and SDMALEN registers in the System

Interface are not defined after a system bus error.

C. In cycle-steal mode, state TX is present on every system bus transfer. In burst mode, state TX is present on the first bus transfer

and whenever the increment of the DMA Address Register carries beyond the least significant 16 bits.

D. SDTACK

is not sampled to verify that it is deasserted.

E. Unless otherwise specified, for all signals specified as a maximum delay from the end of an SBCLK transition to the signal valid,

the signal is also specified to hold its previous value (including high-impedance) until the start of that SBCLK transition.

Figure 36. 80x8x Mode Bus Release Timing