www.vxitech.com

VM4016 Preparation for Use 13

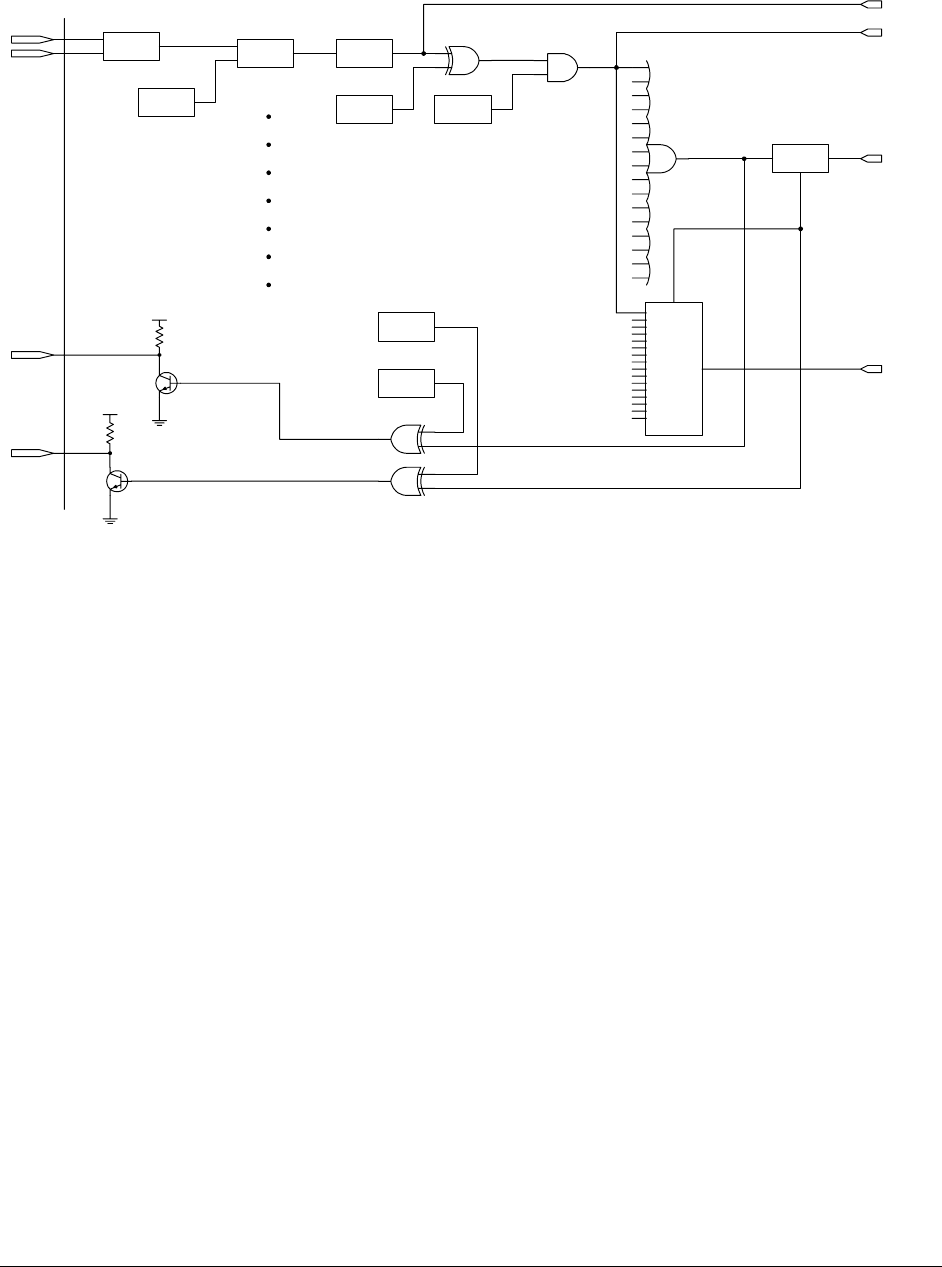

DEBOUNCE

10 uS TO 0.5 S

DIFFERENTIAL

AMPLIFIER

X1 OR X0.1

COMPARATOR

8 BIT DAC

CH1+

CH1-

INVERT

REGISTER

MASK

REGISTER

INTERRUPT

AND FIRST

LIMIT LOGIC

FIRST LIMIT

LATCH

REGISTER

TO VXIBUS

COMPARE

REGISTERS

VXIbus

INTERRUPT

TO VXIBUS

FIRST LIMIT

REGISTER

IRQ

L IRQ

INTERRUPT

INVERT

REGISTER

FIRST LIMIT

INVERT

REGISTER

V

XI MODULE

PANEL

CHANNEL 1 OF

CHANNEL 16 OF

+5V

+5V

FIGURE 1-3: VM4016 BLOCK DIAGRAM