16 www.xilinx.com ML605 Hardware User Guide

UG534 (v1.2.1) January 21, 2010

Chapter 1: ML605 Evaluation Board

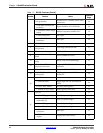

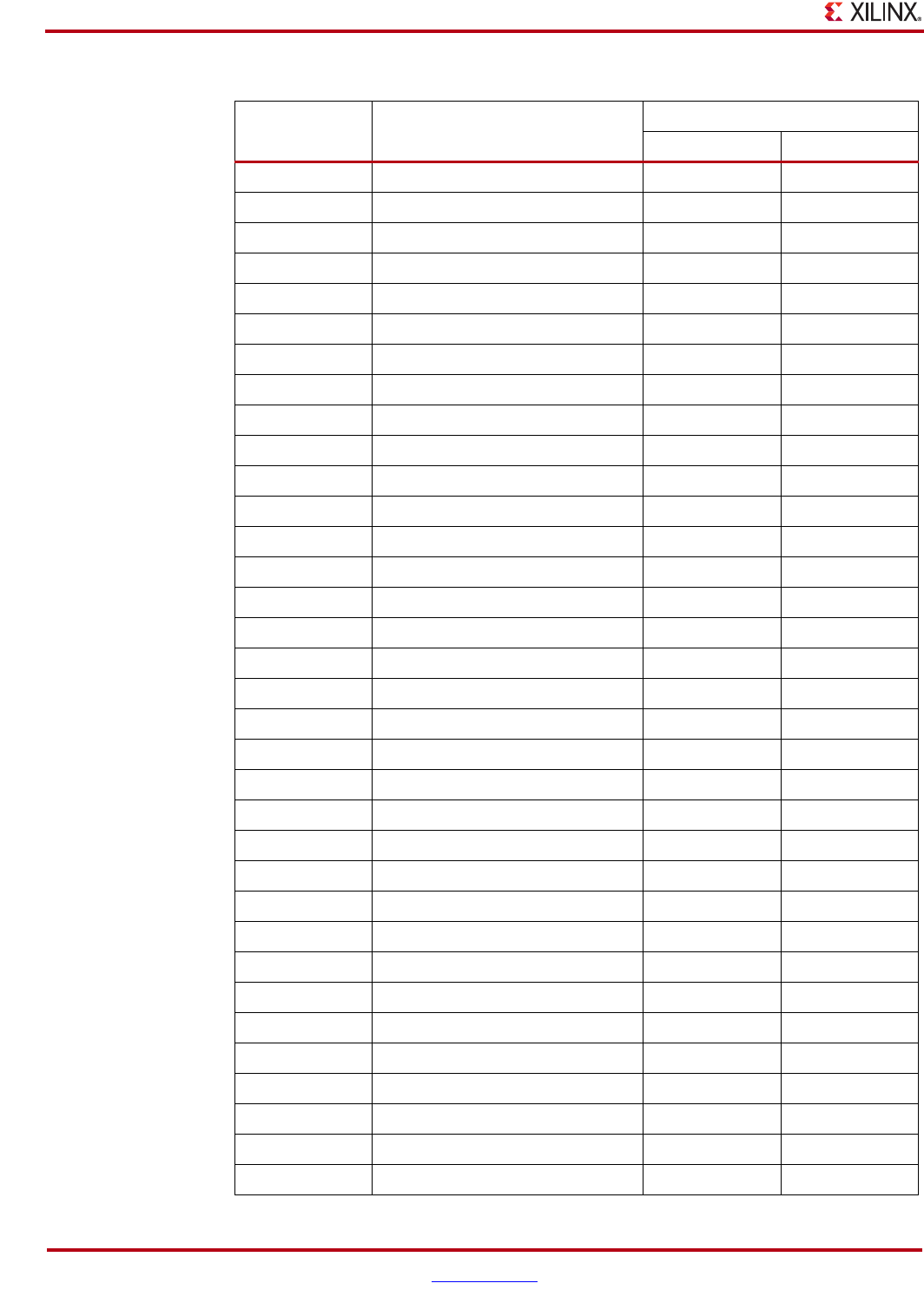

A15 DDR3_A6 90 A6

B15 DDR3_A7 86 A7

G15 DDR3_A8 89 A8

F15 DDR3_A9 85 A9

M16 DDR3_A10 107 A10/AP

M15 DDR3_A11 84 A11

H15 DDR3_A12 83 A12_BC_N

J15 DDR3_A13 119 A13

D15 DDR3_A14 80 A14

C15 DDR3_A15 78 A15

K19 DDR3_BA0 109 BA0

J19 DDR3_BA1 108 BA1

L15 DDR3_BA2 79 BA2

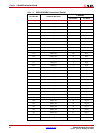

J11 DDR3_D0 5 DQ0

E13 DDR3_D1 7 DQ1

F13 DDR3_D2 15 DQ2

K11 DDR3_D3 17 DQ3

L11 DDR3_D4 4 DQ4

K13 DDR3_D5 6 DQ5

K12 DDR3_D6 16 DQ6

D11 DDR3_D7 18 DQ7

M13 DDR3_D8 21 DQ8

J14 DDR3_D9 23 DQ9

B13 DDR3_D10 33 DQ10

B12 DDR3_D11 35 DQ11

G10 DDR3_D12 22 DQ12

M11 DDR3_D13 24 DQ13

C12 DDR3_D14 34 DQ14

A11 DDR3_D15 36 DQ15

G11 DDR3_D16 39 DQ16

F11 DDR3_D17 41 DQ17

D14 DDR3_D18 51 DQ18

C14 DDR3_D19 53 DQ19

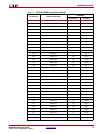

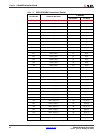

Table 1-4: DDR3 SODIMM Connections (Cont’d)

U1 FPGA Pin Schematic Net Name

J1 SODIMM

Pin Number Pin Name