ML605 Hardware User Guide www.xilinx.com 17

UG534 (v1.2.1) January 21, 2010

Detailed Description

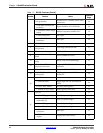

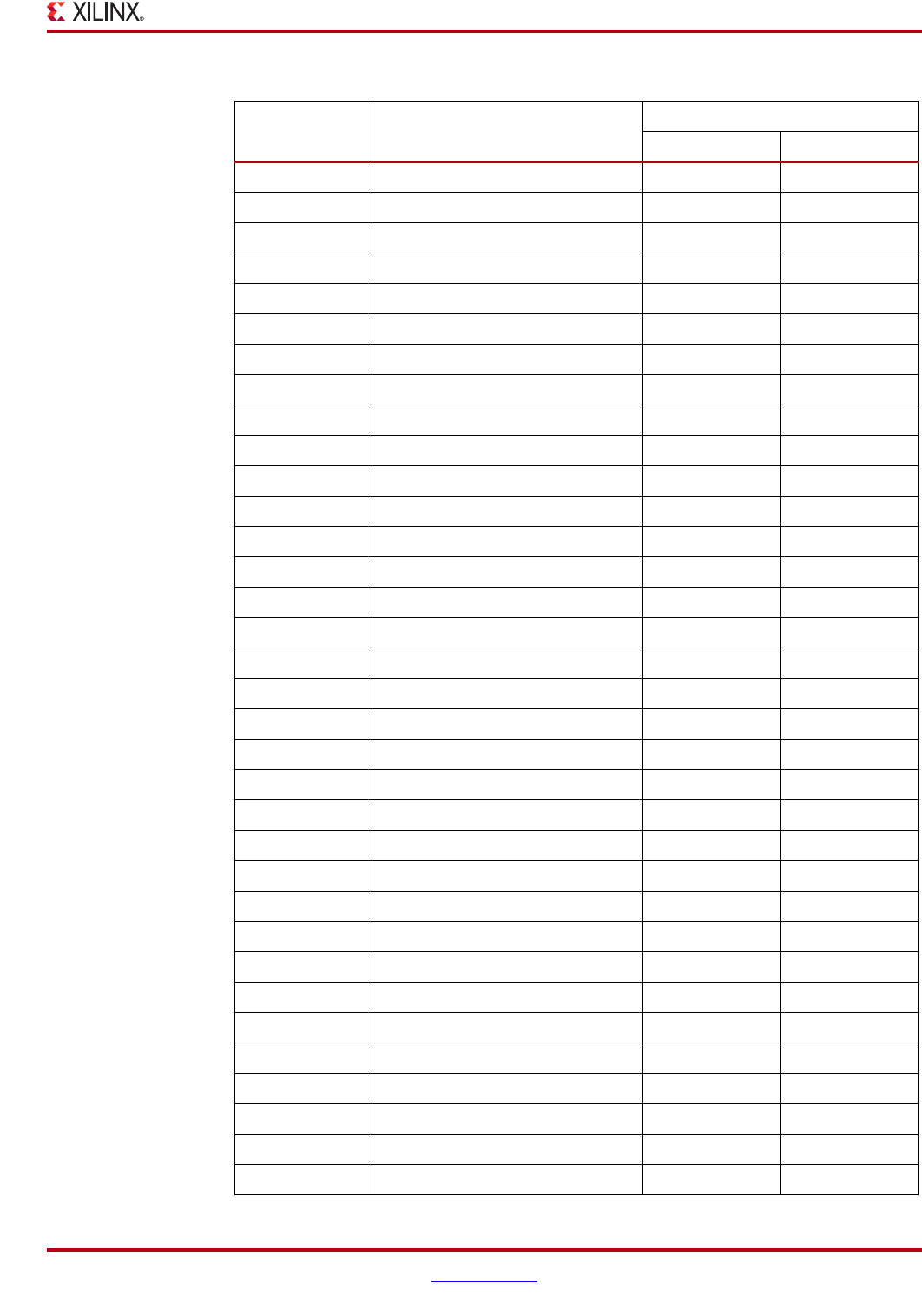

G12 DDR3_D20 40 DQ20

G13 DDR3_D21 42 DQ21

F14 DDR3_D22 50 DQ22

H14 DDR3_D23 52 DQ23

C19 DDR3_D24 57 DQ24

G20 DDR3_D25 59 DQ25

E19 DDR3_D26 67 DQ26

F20 DDR3_D27 69 DQ27

A20 DDR3_D28 56 DQ28

A21 DDR3_D29 58 DQ29

E22 DDR3_D30 68 DQ30

E23 DDR3_D31 70 DQ31

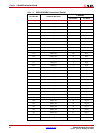

G21 DDR3_D32 129 DQ32

B21 DDR3_D33 131 DQ33

A23 DDR3_D34 141 DQ34

A24 DDR3_D35 143 DQ35

C20 DDR3_D36 130 DQ36

D20 DDR3_D37 132 DQ37

J20 DDR3_D38 140 DQ38

G22 DDR3_D39 142 DQ39

D26 DDR3_D40 147 DQ40

F26 DDR3_D41 149 DQ41

B26 DDR3_D42 157 DQ42

E26 DDR3_D43 159 DQ43

C24 DDR3_D44 146 DQ44

D25 DDR3_D45 148 DQ45

D27 DDR3_D46 158 DQ46

C25 DDR3_D47 160 DQ47

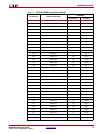

C27 DDR3_D48 163 DQ48

B28 DDR3_D49 165 DQ49

D29 DDR3_D50 175 DQ50

B27 DDR3_D51 177 DQ51

G27 DDR3_D52 164 DQ52

A28 DDR3_D53 166 DQ53

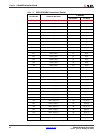

Table 1-4: DDR3 SODIMM Connections (Cont’d)

U1 FPGA Pin Schematic Net Name

J1 SODIMM

Pin Number Pin Name