ML605 Hardware User Guide www.xilinx.com 31

UG534 (v1.2.1) January 21, 2010

Detailed Description

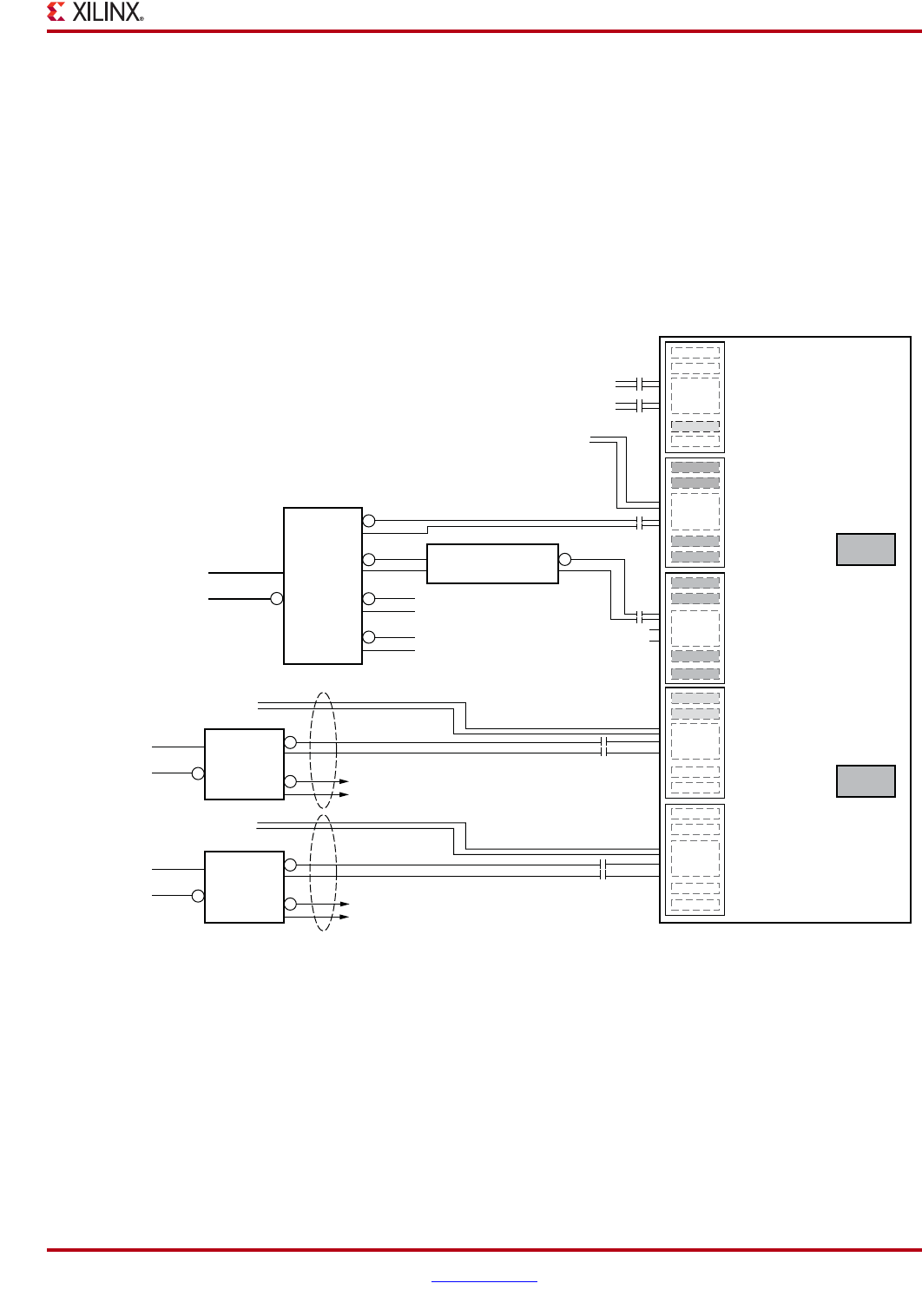

8. Multi-Gigabit Transceivers (GTX MGTs)

The ML605 provides access to 20 MGTs.

• Eight (8) of the MGTs are wired to the PCIe x8 Endpoint (P1) edge connector fingers

• Eight (8) of the MGTs are wired to the FMC HPC connector (J64)

• One (1) MGT is wired to SMA connectors (J26, J27)

• One (1) MGTs is wired to the FMC LPC connector (J63)

• One (1) MGT is wired to the SFP Module connector (P4)

• One (1) MGT is used for an SGMII connection to the Ethernet PHY (U80)

References

See the Virtex-6 FPGA GTX Transceivers User Guide. [Ref 12]

X-Ref Target - Figure 1-10

Figure 1-10: MGT Clocking

ICS

854104

100 MHz LVDS

100 MHz in from

No Connect

No Connect

No Connect

PCIe Fingers

(HCSL)

250 MHz LVDS

GTX_X0Y19

GTX_X0Y18

GTX_X0Y17

GTX_X0Y16

GTX_X0Y15

GTX_X0Y14

GTX_X0Y13

GTX_X0Y12

GTX_X0Y11

GTX_X0Y10

GTX_X0Y09

GTX_X0Y08

GTX_X0Y07

GTX_X0Y06

GTX_X0Y05

GTX_X0Y04

GTX_X0Y03

GTX_X0Y02

GTX_X0Y01

GTX_X0Y00

PCIe

PCIe

BANK_115BANK_114BANK_113BANK_112 BANK_116

SGMII

SMA

SFP

FMC#2

PCIe Lane1

PCIe Lane 2

PCIe Lane 3

PCIe Lane 4

PCIe Lane 5

PCIe Lane 6

PCIe Lane 7

PCIe Lane 8

FMC#1

FMC#1

FMC#1

FMC#1

FMC#1

FMC#1

FMC#1

FMC#1

SMA xxx MHz LVDS

FMC#2 LPC xxxMHz GBTCLK0 LVDS

AC coupling on Mezz

SGMII 125 MHz LVDS

FMC#1 HPC xxx MHz LVDS GBTCLK0

REFCLK0

REFCLK1

REFCLK0

REFCLK1

REFCLK0

REFCLK1

REFCLK0

REFCLK1

REFCLK0

REFCLK1

AC coupling on Mezz

ICS

854104

(LVDS)

ICS

854104

(LVDS)

FMC#1 HPC CLK3_M2C

To FPGA CLK3_M2C_IO CC pin

FMC#1 HPC CLK2_M2C

To FPGA CLK2_M2C_IO CC pin

AC coupling on Mezz

FMC#1 HPC xxx MHz LVDS GBTCLK1

(LVDS)

(LVDS)

UG534_10_101409

Note: xxxMHz = user specified frequency

ICS874001