ML605 Hardware User Guide www.xilinx.com 35

UG534 (v1.2.1) January 21, 2010

Detailed Description

References

See the following websites for more Virtex-6 FPGA Integrated Endpoint Block for PCI

Express information:

• http://www.xilinx.com/products/ipcenter/V6_PCI_Express_Block.htm

• http://www.xilinx.com/support/documentation/ipbusinterfacei-o_pci-

express_v6pciexpressendpointblock.htm

In addition, see the PCI Express specifications for more information. [Ref 27]

10. SFP Module Connector

The board contains a small form-factor pluggable (SFP) connector and cage assembly that

accepts SFP modules. The SFP interface is connected to MGT Bank 116 on the FPGA. The

SFP module serial ID interface is connected to the "SFP" IIC bus (see “15. IIC Bus,” page 42

for more information). The control and status signals for the SFP module are connected to

jumpers and test points as described in Table 1-9. The SFP module connections are shown

in Table 1-10, page 36.

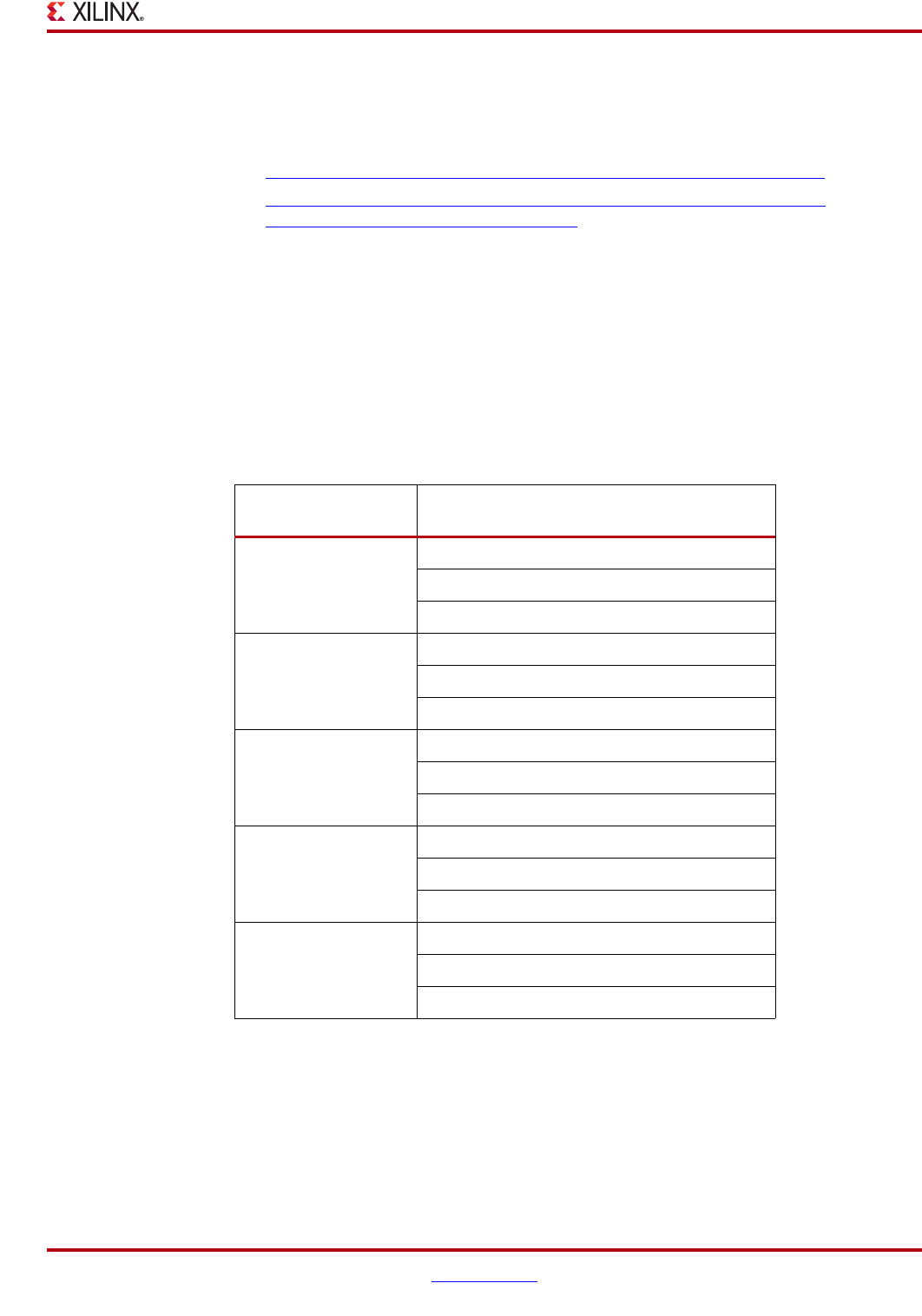

Table 1-9: SFP Module Control and Status

SFP Control/Status

Signal

Board Connection

SFP_TX_FAULT

Test Point J52

High = Fault

Low = Normal Operation

SFP_TX_DISABLE

Jumper J65

Off = SFP Disabled

On = SFP Enabled

SFP_MOD_DETECT

Test Point J53

High = Module Not Present

Low = Module Present

SFP_RT_SEL

Jumper J54

Jumper Pins 1-2 = Full Bandwidth

Jumper Pins 2-3 = Reduced Bandwidth

SFP_LOS

Test Point J51

High = Loss of Receiver Signal

Low = Normal Operation