58 www.xilinx.com ML605 Hardware User Guide

UG534 (v1.2.1) January 21, 2010

Chapter 1: ML605 Evaluation Board

Note: The ML605 board VADJ voltage for the FMC HPC and LPC connectors (J64 and J63) is fixed

at 2.5V (non-adjustable). The 2.5V rail cannot be turned off. The ML605 VITA 57.1 FMC interfaces

are compatible with 2.5V mezzanine cards capable of supporting 2.5V VADJ.

Table 1-28 shows the VITA 57.1 FMC HPC connections. The connector pinout is in

Appendix B, “VITA 57.1 FMC LPC (J63) and HPC (J64) Connector Pinout.”

Any signal named FMC_HPC_xxxx that is wired between a U1 FPGA pin and some other

device does not appear in this table.

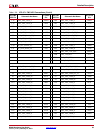

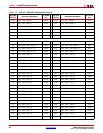

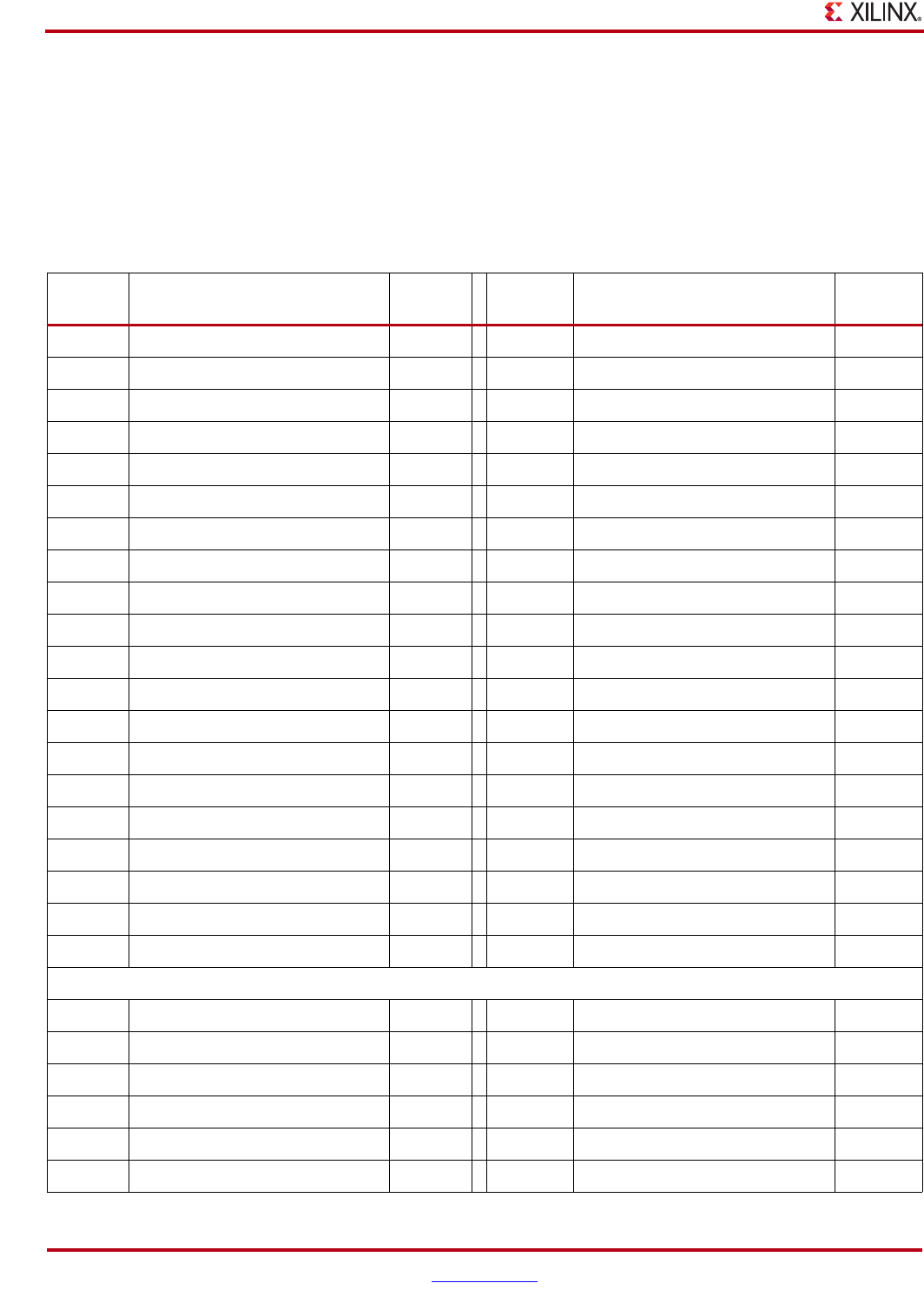

Table 1-28: VITA 57.1 FMC HPC Connections

J64 FMC

HPC Pin

Schematic Net Name

U1 FPGA

Pin

J64 FMC

HPC Pin

Schematic Net Name

U1 FPGA

Pin

A2 FMC_HPC_DP1_M2C_P AE3 B12 FMC_HPC_DP7_M2C_P AP5

A3 FMC_HPC_DP1_M2C_N AE4 B13 FMC_HPC_DP7_M2C_N AP6

A6 FMC_HPC_DP2_M2C_P AF5 B16 FMC_HPC_DP6_M2C_P AM5

A7 FMC_HPC_DP2_M2C_N AF6 B17 FMC_HPC_DP6_M2C_N AM6

A10 FMC_HPC_DP3_M2C_P AG3 B20 FMC_HPC_GBTCLK1_M2C_P AK6

A11 FMC_HPC_DP3_M2C_N AG4 B21 FMC_HPC_GBTCLK1_M2C_N AK5

A14 FMC_HPC_DP4_M2C_P AJ3 B32 FMC_HPC_DP7_C2M_P AP1

A15 FMC_HPC_DP4_M2C_N AJ4 B33 FMC_HPC_DP7_C2M_N AP2

A18 FMC_HPC_DP5_M2C_P AL3 B36 FMC_HPC_DP6_C2M_P AN3

A19 FMC_HPC_DP5_M2C_N AL4 B37 FMC_HPC_DP6_C2M_N AN4

A22 FMC_HPC_DP1_C2M_P AD1

A23 FMC_HPC_DP1_C2M_N AD2

A26 FMC_HPC_DP2_C2M_P AF1

A27 FMC_HPC_DP2_C2M_N AF2

A30 FMC_HPC_DP3_C2M_P AH1

A31 FMC_HPC_DP3_C2M_N AH2

A34 FMC_HPC_DP4_C2M_P AK1

A35 FMC_HPC_DP4_C2M_N AK2

A38 FMC_HPC_DP5_C2M_P AM1

A39 FMC_HPC_DP5_C2M_N AM2

C2 FMC_HPC_DP0_C2M_P AB1 D4 FMC_HPC_GBTCLK0_M2C_P AD6

C3 FMC_HPC_DP0_C2M_N AB2 D5 FMC_HPC_GBTCLK0_M2C_N AD5

C6 FMC_HPC_DP0_M2C_P AC3 D8 FMC_HPC_LA01_CC_P AK19

C7 FMC_HPC_DP0_M2C_N AC4 D9 FMC_HPC_LA01_CC_N AL19

C10 FMC_HPC_LA06_P AG20 D11 FMC_HPC_LA05_P AG22

C11 FMC_HPC_LA06_N AG21 D12 FMC_HPC_LA05_N AH22