32 www.xilinx.com ML605 Hardware User Guide

UG534 (v1.2.1) January 21, 2010

Chapter 1: ML605 Evaluation Board

9. PCI Express Endpoint Connectivity

The 8-lane PCIe edge connector performs data transfers at the rate of 2.5 GT/s for a Gen1

application and 5.0 GT/s for a Gen2 application. The Virtex FPGA GTX MGTs are used for

the multi-gigabit per second serial interfaces.

The ML605 board trace impedance on all PCIe lanes supports both Gen1 and Gen2

applications. The ML605 supports up to Gen1 x8 and Gen2 x4 as shipped with a -1 speed

grade for the LX240T device.

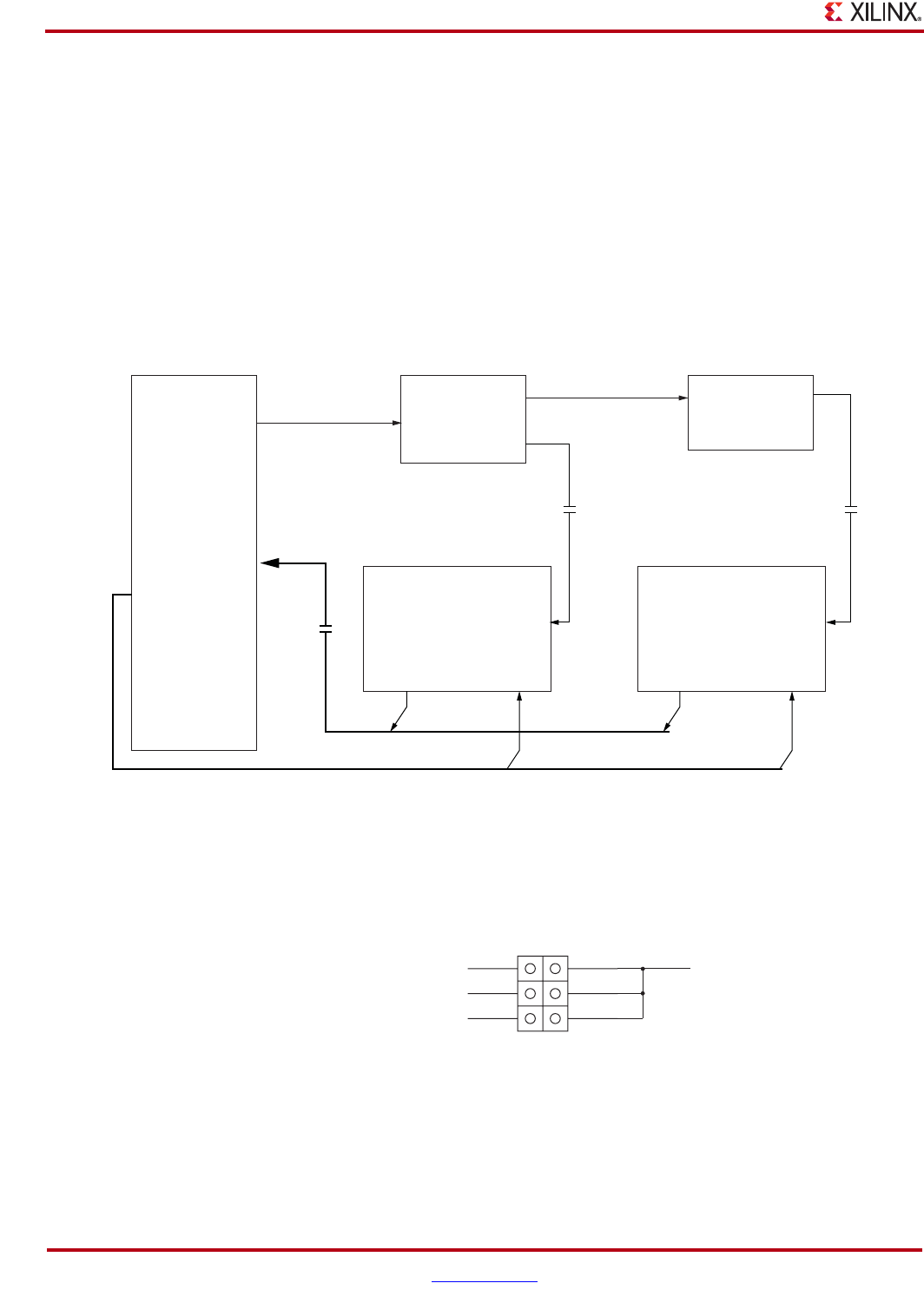

Figure 1-11, page 32 is a diagram of the PCIe MGT bank 114 and 115 clocking.

PCIe lane width/size is selected via jumper J42 as shown in Figure 1-12. The default lane

size selection is 1-lane (J42 pins 1 and 2 jumpered).

X-Ref Target - Figure 1-11

Figure 1-11: PCIe MGT Banks 114 and 115 Clocking

UG534_11_100809

P1

U1

Bank 115

ICS874001

ICS854104

REFCLK+,-

PERp,n[7:0]

PCIE_TX[7:0]_P/N

PCIE_RX[7:0]_P/N

MGTREFCLK0 P/N

PETp,n[7:0]

PCIE_CLK_Q0_P/N

Note: PCIe edge connector signal nomenclature is

from perspective of the system/motherboard.

PCIE_100M_MGT1_P/N

PCIE_100M_MGT0_P/N

PCIE_100M_MGT0_C_P/N PCIE_250M_MGT1_C_P/N

PCIE_250M_MGT1_P/N

CLK/NCLK

PCIe

8-Lane

Edge

Connector

MGTTX

P/N[3:0]

MGTRX

P/N[3:0]

U1

Bank 114

MGTREFCLK0 P/N

MGTTX

P/N[7:4]

MGTRX

P/N[7:4]

U14

Q1/NQ1

Q0/NQ0

CLK/NCLK

U9

Q/NQ

X-Ref Target - Figure 1-12

Figure 1-12: PCIe Lane Size Select Jumper J42

J42

1

2

3

4

5

6

H-2X3

PCIE_PRSNT_B

PCIE_PRSNT_X8

PCIE_PRSNT_X4

PCIE_PRSNT_X1

UG534_12_111709