ML605 Hardware User Guide www.xilinx.com 33

UG534 (v1.2.1) January 21, 2010

Detailed Description

Table 1-8 shows the PCIe connector (P1) that provides up to 8-lane access through the GTX

transceivers to the Virtex-6 FPGA integrated Endpoint block for PCIe designs.

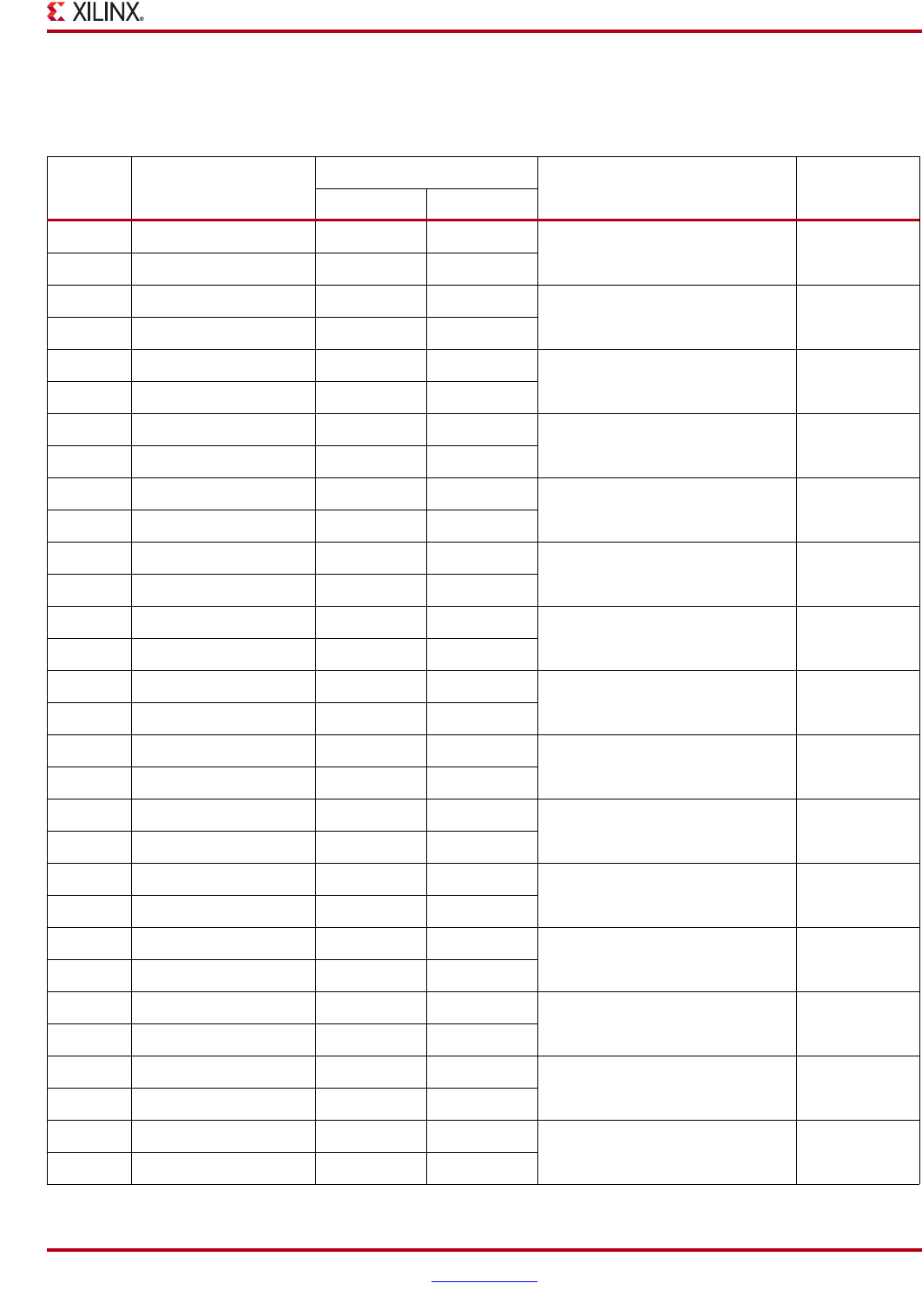

Table 1-8: PCIe Edge Connector Connections

U1 FPGA

Pin

Schematic Net Name

P1 PCIe Edge Connector

Description

Package

Placement

Pin Number Pin Name

F1 PCIE_TXO_P A16 PERp0

Integrated Endpoint block

transmit pair

GTXE1_X0Y15

F2 PCIE_TXO_N A17 PERn0

H1 PCIE_TX1_P A21 PERp1

Integrated Endpoint block

transmit pair

GTXE1_X0Y14

H2 PCIE_TX1_N A22 PERn1

K1 PCIE_TX2_P A25 PERp2

Integrated Endpoint block

transmit pair

GTXE1_X0Y13

K2 PCIE_TX2_N A26 PERn2

M1 PCIE_TX3_P A29 PERp3

Integrated Endpoint block

transmit pair

GTXE1_X0Y11

M2 PCIE_TX3_N A30 PERn3

P1 PCIE_TX4_P A35 PERp4

Integrated Endpoint block

transmit pair

GTXE1_X0Y10

P2 PCIE_TX4_N A36 PERn4

T1 PCIE_TX5_P A39 PERp5

Integrated Endpoint block

transmit pair

GTXE1_X0Y9

T2 PCIE_TX5_N A40 PERn5

V1 PCIE_TX6_P A43 PERp6

Integrated Endpoint block

transmit pair

GTXE1_X0Y8

V2 PCIE_TX6_N A44 PERn6

Y1 PCIE_TX7_P A47 PERp7

Integrated Endpoint block

transmit pair

GTXE1_X0Y7

Y2 PCIE_TX7_N A48 PERn7

J3 PCIE_RXO_P B14 PETp0

Integrated Endpoint block

receive pair

GTXE1_X0Y15

J4 PCIE_RXO_N B15 PETn0

K5 PCIE_RX1_P B19 PETp1

Integrated Endpoint block

receive pair

GTXE1_X0Y14

K6 PCIE_RX1_N B20 PETn1

L3 PCIE_RX2_P B23 PETp2

Integrated Endpoint block

receive pair

GTXE1_X0Y13

L4 PCIE_RX2_N B24 PETn2

N3 PCIE_RX3_P B27 PETp3

Integrated Endpoint block

receive pair

GTXE1_X0Y11

N4 PCIE_RX3_N B28 PETn3

R3 PCIE_RX4_P B33 PETp4

Integrated Endpoint block

receive pair

GTXE1_X0Y10

R4 PCIE_RX4_N B34 PETn4

U3 PCIE_RX5_P B37 PETp5

Integrated Endpoint block

receive pair

GTXE1_X0Y9

U4 PCIE_RX5_N B38 PETn5

W3 PCIE_RX6_P B41 PETp6

Integrated Endpoint block

receive pair

GTXE1_X0Y8

W4 PCIE_RX6_N B42 PETn6