CY7C67300

Document #: 38-08015 Rev. *J Page 87 of 99

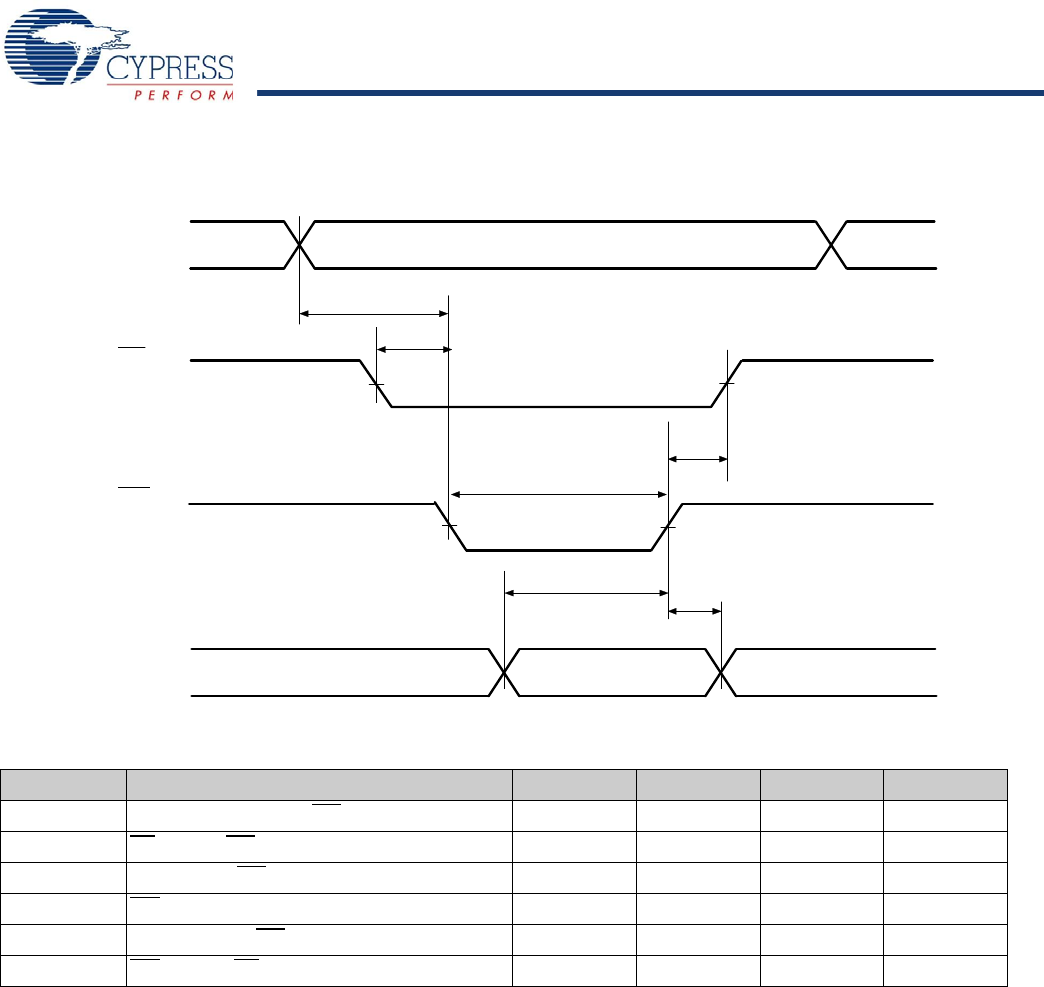

SRAM Write Cycle

[17]

Notes

16. t

WPW

The write pulse width = 18.8 ns min. for zero and one wait states. The write pulse = 18.8 ns + (n – 1)*T for wait states = n, n > 1, T = 48 MHz clock period.

17. Write timing is applicable for nXMEMSEL, nXRAMSEL and nXROMSEL.

Table 138. SRAM Write Cycle Parameters

Parameter Description Min Typical Max Unit

t

AW

Write Address Valid to WE LOW 7 ns

t

CSW

CS LOW to WE LOW 7 ns

t

DW

Data Valid to WE HIGH 15 ns

t

WPW

[16]

WE Pulse Width 15 ns

t

DH

Data Hold from WE HIGH 4.5 ns

t

WC

WE HIGH to CS HIGH 13 ns

Address

CS

WE

Dout

t

AW

t

CSW

t

WPW

t

DW

t

WC

t

DH

Data Valid

[+] Feedback