CY7C67300

Document #: 38-08015 Rev. *J Page 92 of 99

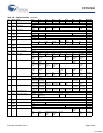

Hardware CTS/RTS Handshake

t

CTSsetup

: HSS_CTS setup time before HSS_RTS = 1.5T min.

t

CTShold

: HSS_CTS hold time after START bit = 0 ns min.

T = 1/48 MHz.

When RTS/CTS hardware handshake is enabled, transmission can be help off by deasserting HSS_CTS at least 1.5T before

HSS_RTS. Transmission resumes when HSS_CTS returns HIGH. HSS_CTS must remain HIGH until START bit.

HSS_RTS is deasserted in the third data bit time.

An application may choose to hold HSS_CTS until HSS_RTS is deasserted, which always occurs after the START bit.

Register Summary

tCTSsetup

tCTSsetup

Start of transmission delayed until HSS_CTS goes high

Start of transmission not delayed by HSS_CTS

tCTShold

tCTShold

HSS_RTS

HSS_CTS

HSS_TxD

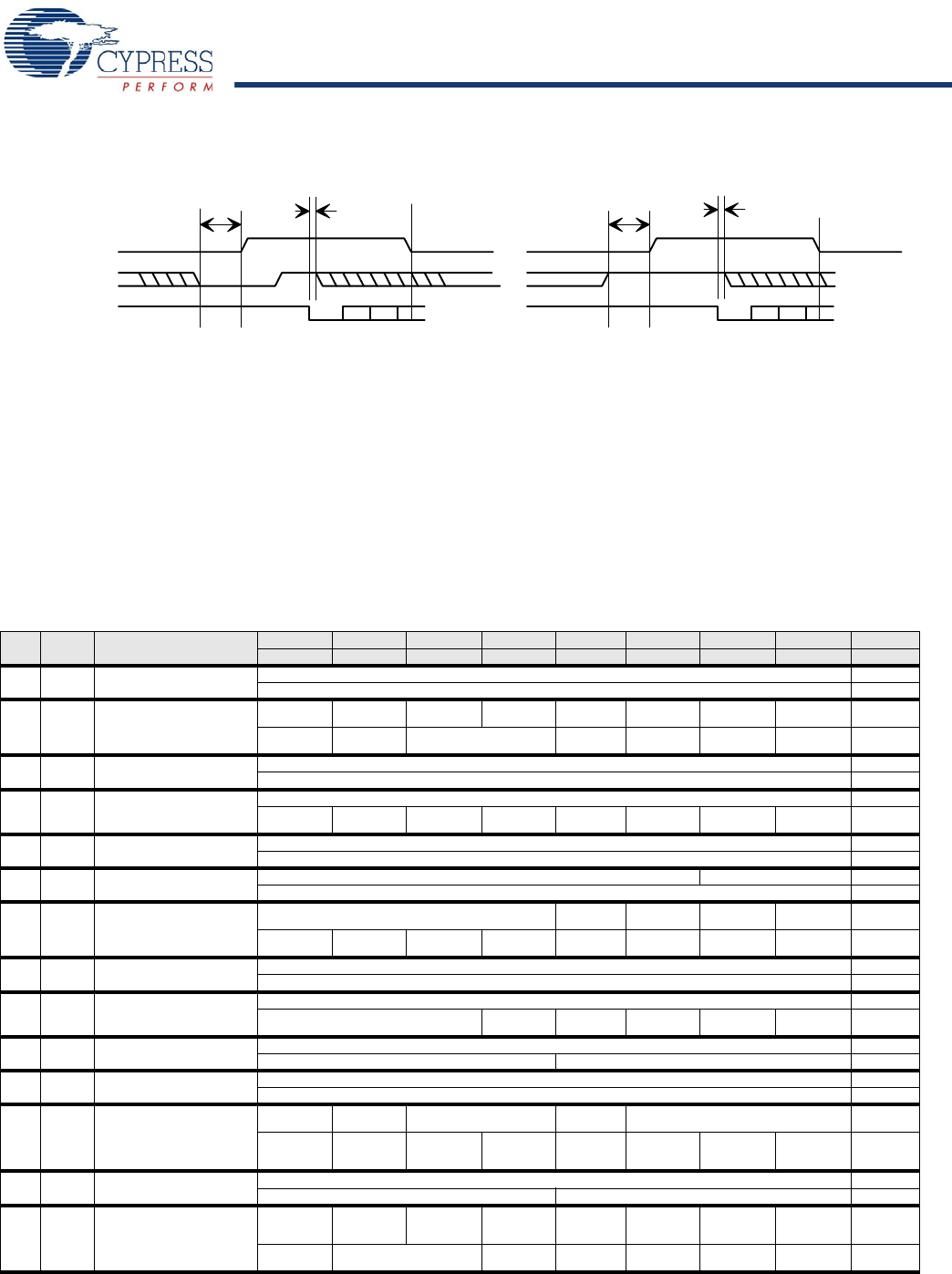

Table 142. Register Summary

R/W Address Register Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Default High

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Default Low

R 0x0140 HPI Breakpoint Address... 0000 0000

...Address 0000 0000

R 0x0142 Interrupt Routing VBUS to HPI

Enable

ID to HPI

Enable

SOF/EOP2 to

HPI Enable

SOF/EOP2 to

CPU Enable

SOF/EOP1 to

HPI Enable

SOF/EOP1 to

CPU Enable

Reset2 to HPI

Enable

HPI Swap 1

Enable

0001 0100

Resume2 to

HPI Enable

Resume1 to

HPI Enable

Reserved Done2 to HPI

Enable

Done1 to HPI

Enable

Reset1 to HPI

Enable

HPI Swap 0

Enable

0000 0000

W 1: 0x0144

2: 0x0148

SIEXmsg Data... xxxx xxxx

...Data xxxx xxxx

R/W 0x02n0 Device n Endpoint n Control Reserved xxxx xxxx

IN/OUT

Ignore Enable

Sequence

Select

Stall

Enable

ISO

Enable

NAK Interrupt

Enable

Direction

Select

Enable ARM

Enable

xxxx xxxx

R/W 0x02n2 Device n Endpoint n Address Address... xxxx xxxx

...Address xxxx xxxx

R.W 0x02n4 Device n Endpoint n Count Reserved Count... xxxx xxxx

...Count xxxx xxxx

R/W 0x02n6 Device n Endpoint n Status Reserved Overflow

Flag

Underflow

Flag

OUT

Exception Flag

IN

Exception Flag

xxxx xxxx

Stall

Flag

NAK

Flag

Length

Exception Flag

Setup

Flag

Sequence

Status

Timeout

Flag

Error

Flag

ACK

Flag

xxxx xxxx

R/W 0x02n8 Device n Endpoint n Count Result Result... xxxx xxxx

...Result xxxx xxxx

R 0xC000 CPU Flags Reserved... 0000 0000

...Reserved Global Inter-

rupt Enable

Negative

Flag

Overflow

Flag

Carry

Flag

Zero

Flag

000x xxxx

R/W 0xC002 Bank Address... 0000 0001

...Address Reserved 000x xxxx

R 0xC004 Hardware Revision Revision... xxxx xxxx

...Revision xxxx xxxx

R/W 0xC006 GPIO Control Write Protect

Enable

UD Reserved SAS

Enable

Mode

Select

0000 0000

HSS

Enable

HSS XD

Enable

SPI

Enable

SPI XD

Enable

Interrupt 1

Polarity

Select

Interrupt 1

Enable

Interrupt 0

Polarity

Select

Interrupt 0

Enable

0000 0000

R/W 0xC008 CPU Speed Reserved... 0000 0000

.Reserved CPU Speed 0000 1111

R/W 0xC00A Power Control Host/Device

2B Wake

Enable

Host/Device

2A Wake

Enable

Host/Device

1B Wake

Enable

Host/Device

1A Wake

Enable

OTG

Wake

Enable

Reserved HSS

Wake

Enable

SPI

Wake

Enable

0000 0000

HPI

Wake Enable

Reserved GPI

Wake Enable

Reserved Boost 3V

OK

Sleep

Enable

Halt

Enable

0000 0000

[+] Feedback