228

APPENDIX

Notes:

1. In byte transfer to A, T ← A is only low bytes.

2. The operands of an instruction with two or more operands should be stored in the order designated in

MNEMONIC.

41 SETB dir:b 4 2 (dir):b ← 1 – – – – – – – A8 to AF

42 CLRB dir:b 4 2 (dir):b ← 0 – – – – – – – A0 to A7

43 XCH A, T 1 1 (AL) ↔ (TL) AL – – – – – – 42

44 XCHW A, T 1 1 (A) ↔ (T) AL AH dH – – – – 43

45 XCHW A, EP 1 1 (A) ↔ (EP) – – dH – – – – F7

46 XCHW A, IX 1 1 (A) ↔ (IX) – – dH – – – – F6

47 XCHW A, SP 1 1 (A) ↔ (SP) – – dH – – – – F5

48 MOVW A, PC 2 1 (A) ← (PC) – – dH – – – – F0

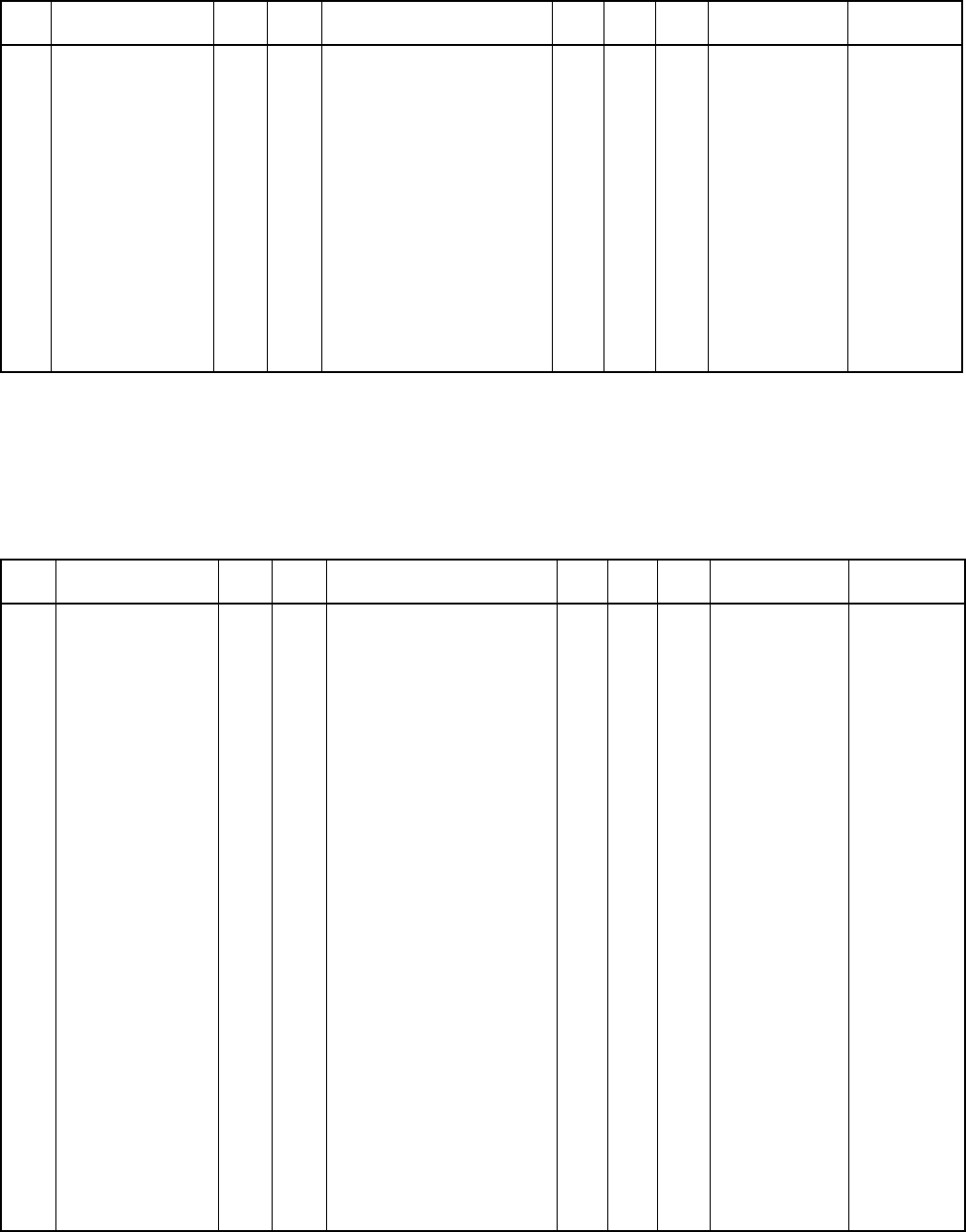

Table A.2-1 Operation List (for Transfer Instructions) (3/3)

No MNEMONIC ~ # OPERATION TL TH AH N Z V C OP CODE

Table A.2-2 Operation List (for Operation Instructions) (1/3)

No MNEMONIC ~ # OPERATION TL TH AH NZVC OP CODE

1ADDC A, Ri 21(A) ← (A)+(Ri)+C – – – + + + + 28 to 2F

2ADDC A, #d8 22(A) ← (A)+d8+C – – – + + + + 24

3ADDC A, dir 32(A) ← (A)+(dir)+C – – – + + + + 25

4ADDC A,

@IX+off

32(A) ← (A)+((IX)+off)+C – – – + + + + 26

5ADDC A, @EP21(A) ← (A)+((EP))+C – – – + + + + 27

6ADDCW A 11(A) ← (A)+(T)+C – – dH + + + + 23

7ADDC A 11(AL) ← (AL)+(TL)+C – – – + + + + 22

8SUBC A, Ri 21(A) ← (A)-(Ri)-C – – – + + + + 38 to 3F

9SUBC A, #d8 22(A) ← (A)-d8-C – – – + + + + 34

10 SUBC A, dir 3 2 (A) ← (A)-(dir)-C – – – + + + + 35

11 SUBC A,

@IX+off

32(A) ← (A)-((IX)+off)-C – – – + + + + 36

12 SUBC A, @EP 2 1 (A) ← (A)-((EP))-C – – – + + + + 37

13 SUBCW A 1 1 (A) ← (T)-(A)-C – – dH + + + + 33

14 SUBC A 1 1 (AL) ← (TL)-(AL)-C – – – + + + + 32