242

APPENDIX

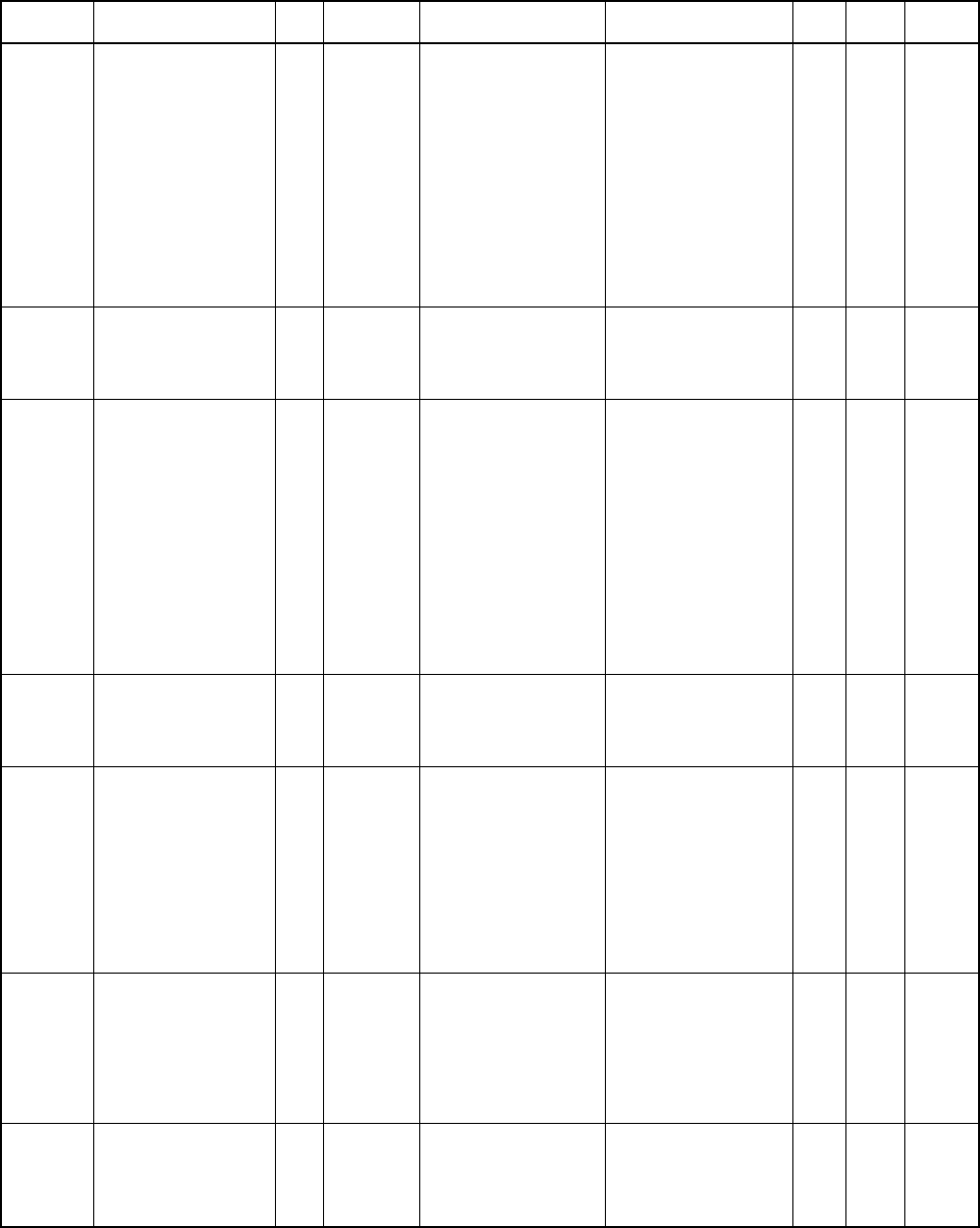

08 - 0F MOV A, Ri 2 1 N +2 The following

following instruction

10 0

18 - 1F CMP A, Ri 2 Rn address Data 1 0 0

28 - 2F ADDC A, Ri

38 - 3F SUBC A, Ri

58 - 5F XOR A, Ri

68 - 6F AND A, Ri

78 - 7F OR A, Ri

48 - 4F MOV Ri, A 2 1 N +2 The following

following instruction

10 0

2 Rn address Data 0 1 0

C0 INCW A 1 1 N +2 The following

following instruction

10 0

D0 DECW A

C1 INCW SP

D1 DECW SP

C2 INCW IX

D2 DECW IX

C3 INCW EP

D3 DECW EP

F0 MOVW A, PC 2 1 N +2 The following

following instruction

10 0

2 −− 00 0

E1 MOVW SP, A 1 1 N +2 The following

following instruction

10 0

F1 MOVW A, SP

E2 MOVW IX, A

F2 MOVW A, IX

E3 MOVW EP, A

F3 MOVW A, EP

E0 JMP @A 3 1 N +2 Data of N +2 1 0 0

2 Address divergence The following

instruction

10 0

3 Address divergence

+1

The following

following instruction

10 0

F5 XCHW A, SP 1 1 N +2 The following

following instruction

10 0

F6 XCHW A, IX

F7 XCHW A, EP

Table B-1 Bus Operation List (3/11)

CODE MNEMONIC ~ Cycle Address bus Data bus RD WR RMW