44

CHAPTER 5 CPU SOFTWARE ARCHITECTURE

■ MULU A

This instruction is used for multiplying 8 bits of the AL by 8 bits of the TL without a sign and stores the 16-

bit result in the accumulator (A). The contents of the temporary accumulator (T) do not change. In the

operation, the original contents of the AH and TH are not used. Since the flag does not change, attention

must be paid to the result of multiplication when branching accordingly.

■ DIVU A

This instruction is used for dividing 16 bits of the temporary accumulator (T) by 16 bits of the A without a

sign and stores the results as 16 bits in the A and the remainder as 16 bits in the T. When A is 0000

H

, Z flag

is 1 as 0 division. At this time, the operation result is not guaranteed.

■ XCHW A, PC

This instruction is used for exchanging the contents of the accumulator (A) for those of the program

counter (PC). As a result, the program branches to the address indicated by the contents of the original

accumulator and the contents of the current accumulator become the value of the address next to the one

where the instruction code XCHW A, PC is stored. This instruction is provided especially for specifying

tables using the main routine and for subroutines to use them.

When this instruction is executed, the contents of the accumulator are the same as those of the address

where the code for the next instruction is stored and not the address where the code for this instruction is

stored. The above example shows that the value of the accumulator 1235

H

agrees with that of the address

where the instruction code next to XCHW A, PC is stored. Consequently, 1235

H

not 1234

H

is indicated.

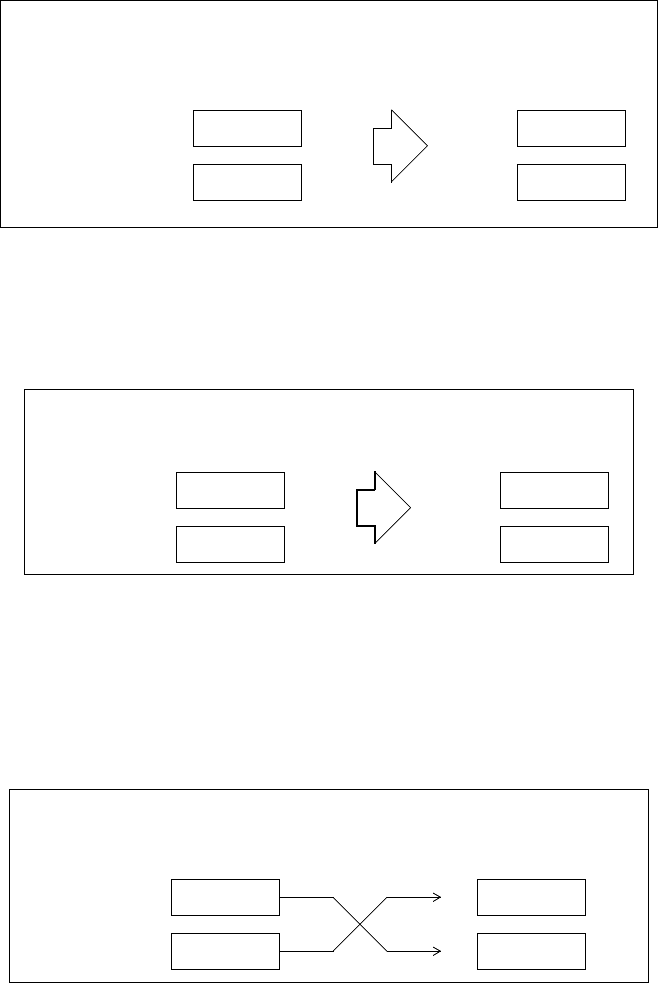

Before execution

After execution

[Example]

MULU A, T

A

A

TT1234

H

1234H

5678H

1860H

Before execution

After execution

[Example]

DIVU A

1234

H

A

A

T

T

5678

H

0004H

0DA8H

Before execution

After execution

[Example]

XCHW A, PC

5678

H

A

PC

A

PC

5678

H

1235H

1234H