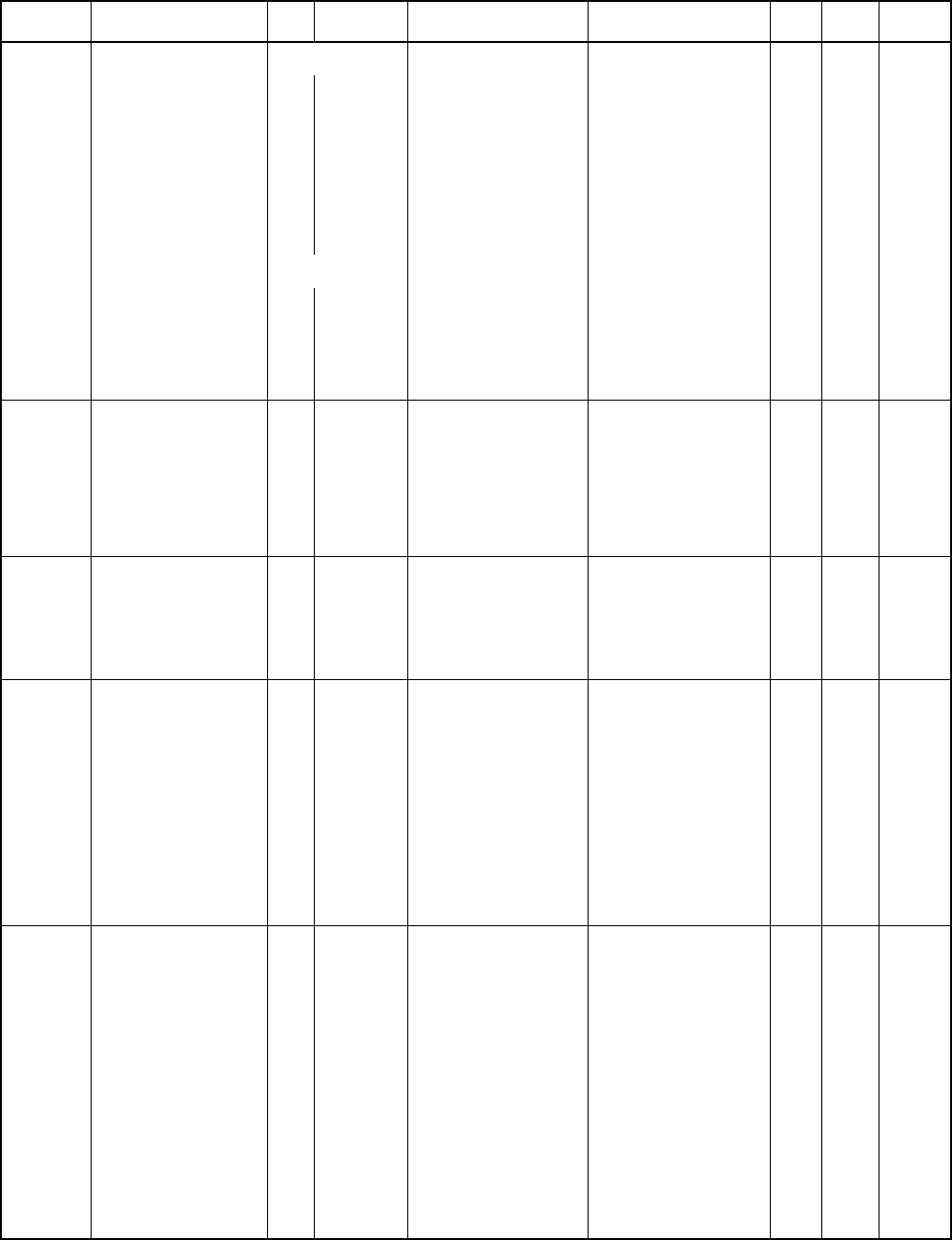

248

APPENDIX

F8 BNC rel Divergence

F9 BC rel 4 1 N +2 Data of N +2 1 0 0

FA BP rel 2 N +3 Data of N +3 1 0 0

FB BN rel 3 Address divergence

ahead

The following

instruction

10 0

FC BNZ rel 4 Address divergence

ahead +1

The following

following instruction

10 0

FD BZ rel No divergence

FE BGE rel 2 1 N +2 The following

instruction

10 0

FF BLT rel 2 N +3 The following

following instruction

10 0

40 PUSHW A 4 1 N +2 The following

following instruction

10 0

41 PUSHW IX 2 −− 00 0

3 SP -1 Save data (L) 0 1 0

4 SP -2 Save data (H) 0 1 0

50 POPW A 3 1 N +2 The following

following instruction

10 0

51 POPW IX 2 SP Return data (H) 1 0 0

3 SP +1 Return data (L) 1 0 0

20 RET 6 1 N +2 Data of N +2 1 0 0

2 SP Return address (H) 1 0 0

3 SP +1 Return address (L) 1 0 0

4 −− 00 0

5Return

address The following

instruction

10 0

6Return

address +1 The following

following instruction

10 0

30 RETI 8 1 N +2 Data of N +2 1 0 0

2SP PSH (RP, DP) 100

3 SP +1 PSL (CCR) 1 0 0

4 SP +2 Return address (H) 1 0 0

5 SP +3 Return address (L) 1 0 0

6 −− 00 0

7Return

address The following

instruction

10 0

8Return

address +1 The following

following instruction

10 0

Table B-1 Bus Operation List (9/11)

CODE MNEMONIC ~ Cycle Address bus Data bus RD WR RMW