243

APPENDIX B Bus Operation List

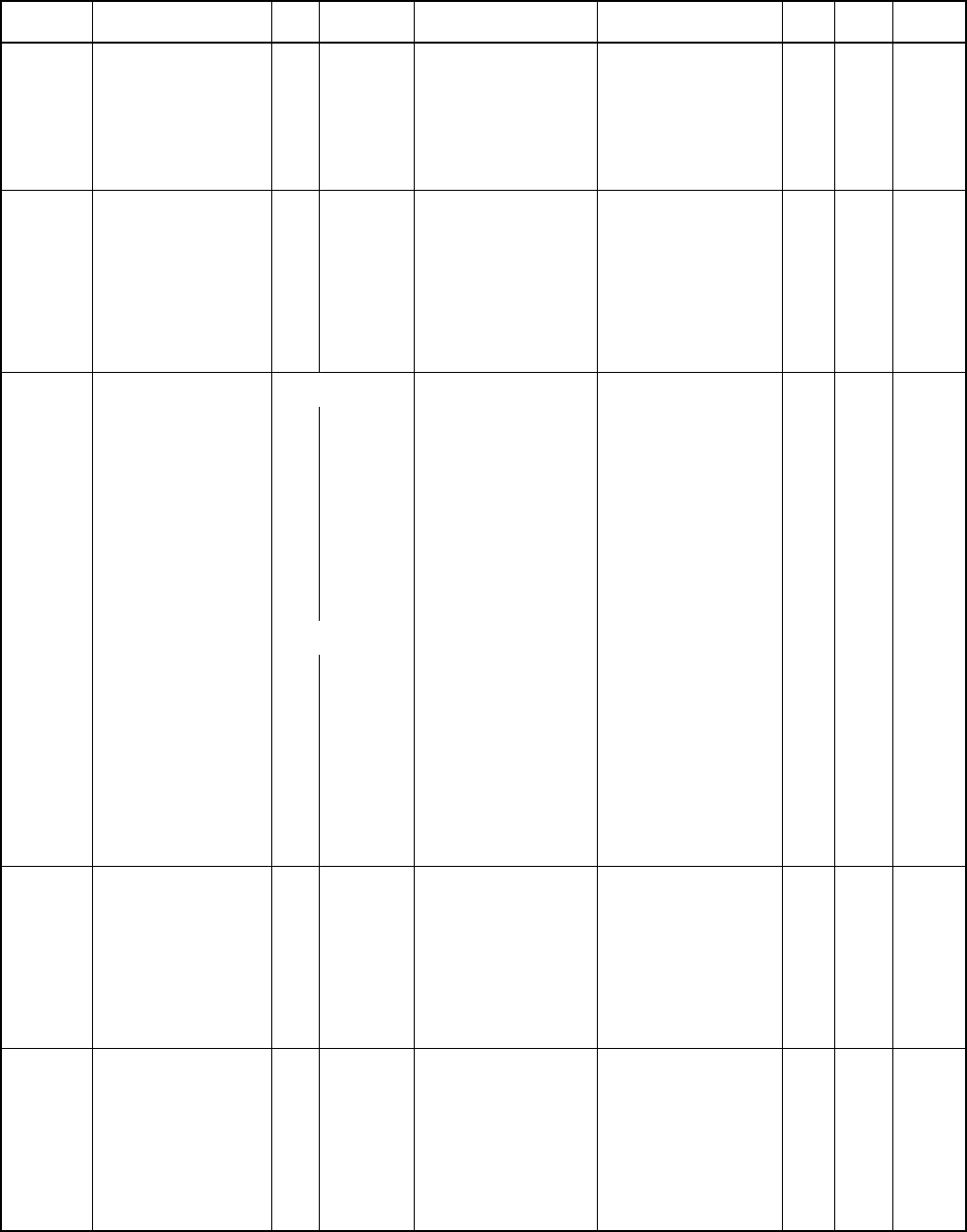

F4 XCHW A, PC 3 1 N +2 Data of N +2 1 0 0

2 Address divergence The following

instruction

10 0

3 Address divergence

+1

The following

following instruction

10 0

A0 - A7 CLRB dir:n 4 1 N +2 The following

instruction

10 1

A8 - AF SETB dir:n 2 dir address Data 1 0 1

3 dir address Data 0 1 0

4 N +3 The following

following instruction

10 0

B0 - B7 BBC dir:n, rel Divergence

B8 - BF BBS dir:n, rel 5 1 N +2 rel 1 0 0

2 dir address Data 1 0 0

3N +3 Data of N+3 100

4 Address divergence The following

instruction

10 0

5 Address divergence

+1

The following

following instruction

10 0

No divergence

51N +2 rel 100

2 dir address Data 1 0 0

3 N +3 The following

instruction

10 0

4 −− 00 0

5 N +4 The following

following instruction

10 0

60 MOV A, ext 4 1 N +2 ext (L byte) 1 0 0

2 N +3 The following

instruction

10 0

3 ext address Data 1 0 0

4 N +4 The following

following instruction

10 0

61 MOV ext, A 4 1 N +2 ext (L byte) 1 0 0

2 N +3 The following

instruction

10 0

3 ext address Data 0 1 0

4 N +4 The following

following instruction

10 0

Table B-1 Bus Operation List (4/11)

CODE MNEMONIC ~ Cycle Address bus Data bus RD WR RMW