41

CHAPTER 5 CPU SOFTWARE ARCHITECTURE

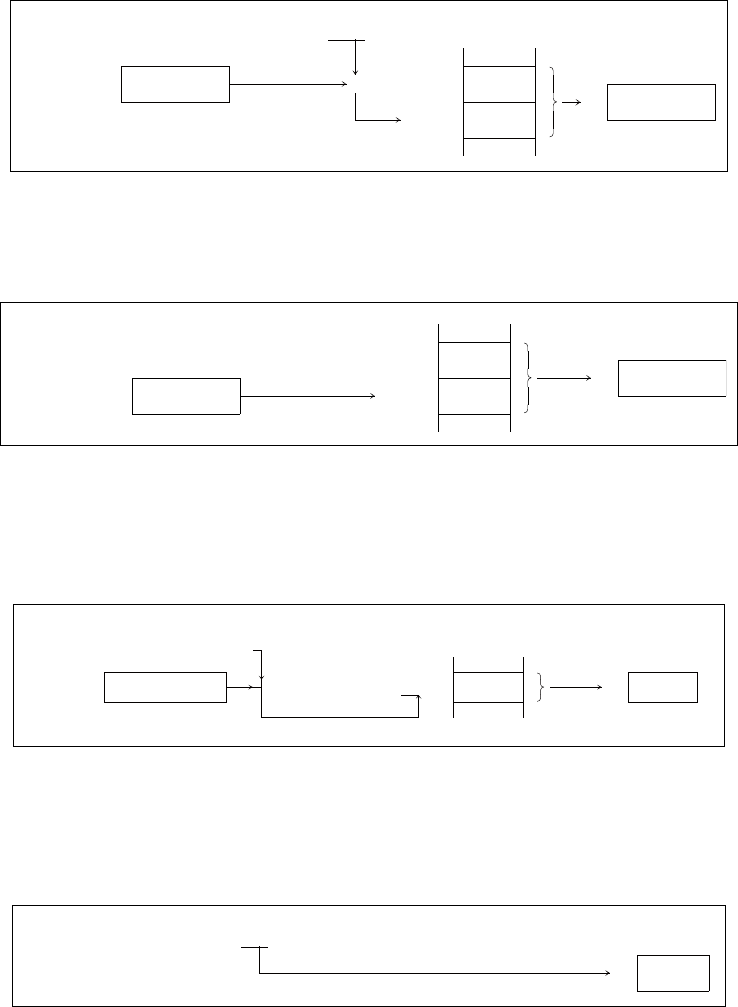

■ Index Addressing (@IX+off)

This addressing mode, indicated as "@IX+off" in the instruction list, is used to access the entire 64-Kbyte

area. In this addressing mode, the contents of the first operand are sign-extended and then added to the

index register (IX). The result is used as the address.

■ Pointer Addressing (@EP)

This addressing mode, indicated as "@EP" in the instruction list, is used to access the entire 64-Kbyte area.

In this addressing mode, the contents of the extra pointer (EP) are used as the address.

■ General-Purpose Register Addressing (Ri)

This addressing mode, indicated as "Ri" in the instruction list, is used to access the register bank area. In

this addressing mode, one upper byte of the address is set to 01 and one lower byte is created from the

contents of the register bank pointer (RP) and the 3 lower bits of the instruction to access this address.

■ Immediate Addressing (#imm)

This addressing mode, indicated as "#imm" in the instruction list, is used for acquiring the immediate data.

In this addressing mode, the operand is used directly as the immediate data. The byte or word is specified

by the instruction code.

IX

34

H

12

H

[Example]

MOVW A, @IX+5AH

27A5

H

2800H

27FFH

1234H

+

A

34H

EP 12H

[Example]

MOVW A, @EP

27A5

H

1234H

27A5H

27A6H

A

RP

[Example] MOV A, R2

01010

B

0152

H

AB

H

AB

H

A

[Example]

MOV A, #56H

A56

H