241

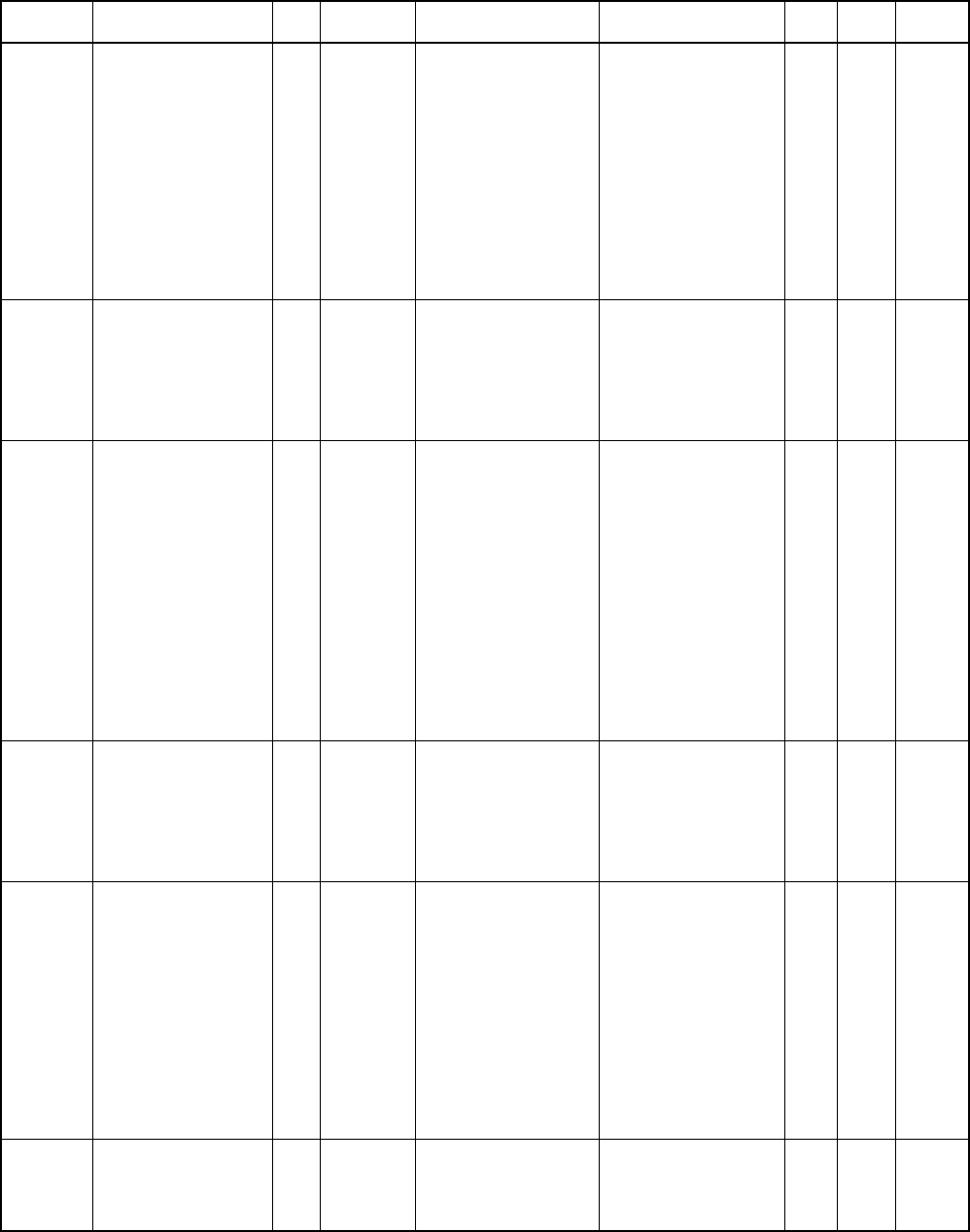

APPENDIX B Bus Operation List

05 MOV A, dir 3 1 N +2 The following

instruction

10 0

15 CMP A, dir 2 dir address Data 1 0 0

25 ADDC A, dir 3 N +3 The following

following instruction

10 0

35 SUBC A, dir

55 XOR A, dir

65 AND A, dir

75 OR A, dir

45 MOV dir, A 3 1 N +2 The following

instruction

10 0

2 dir address Data 0 1 0

3 N +3 The following

following instruction

10 0

06 MOV A, @IX+off 3 1 N +2 The following

instruction

10 0

16 CMP A, @IX+off 2 N +3 The following

following instruction

10 0

26 ADDC A, @IX+off 3 (IX)+off

address

Data 1 0 0

36 SUBC A, @IX+off

56 XOR A, @IX+off

66 AND A, @IX+off

76 OR A, @IX+off

46 MOV @IX+off, A 3 1 N +2 The following

instruction

10 0

2 N +3 The following

following instruction

10 0

3 (IX)+off address Data 0 1 0

07 MOV A, @EP 2 1 N +2 The following

following instruction

10 0

17 CMP A, @EP 2 (EP) address Data 1 0 0

27 ADDC A, @EP

37 SUBC A, @EP

57 XOR A, @EP

67 AND A, @EP

77 OR A, @EP

47 MOV @EP, A 2 1 N +2 The following

following instruction

10 0

2 (EP) address Data 0 1 0

Table B-1 Bus Operation List (2/11)

CODE MNEMONIC ~ Cycle Address bus Data bus RD WR RMW