246

APPENDIX

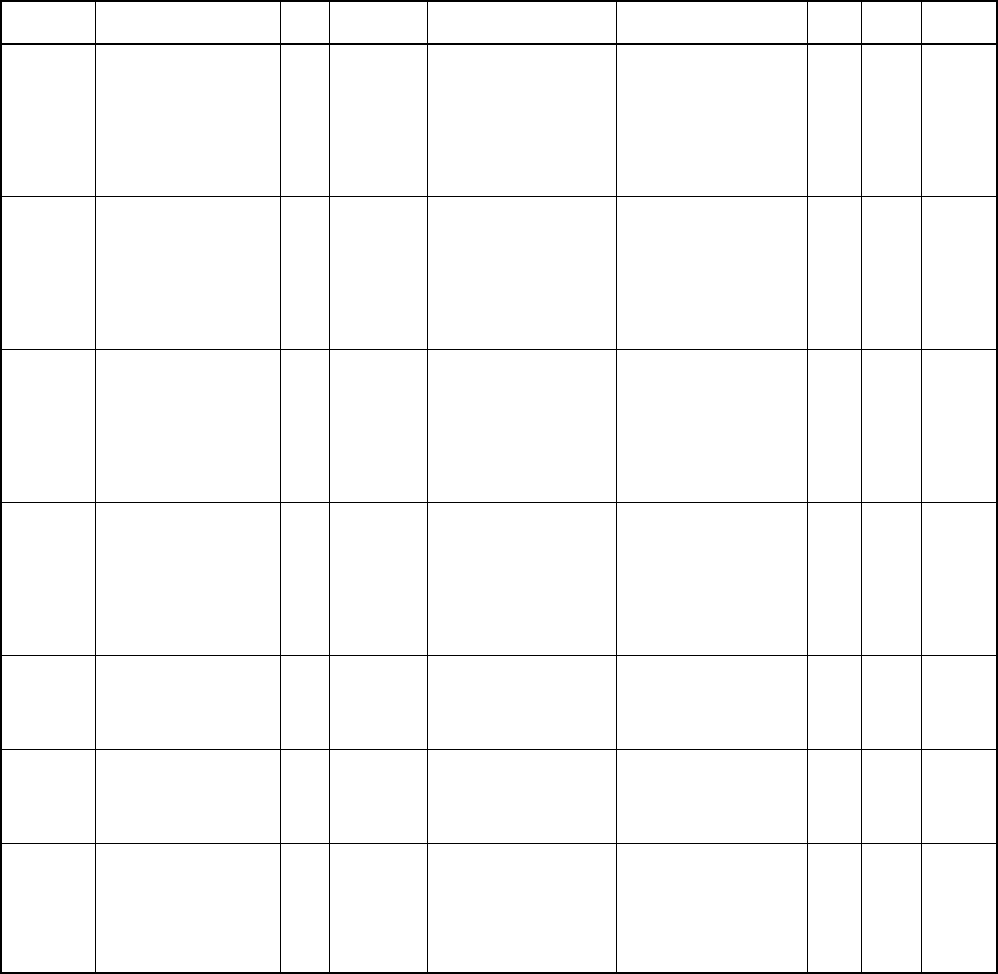

87 MOV @EP, #d8 3 1 N +2 The following

instruction

10 0

2 (EP) address Data 0 1 0

3 N +3 The following

following instruction

10 0

97 CMP @EP, #d8 3 1 N +2 The following

instruction

10 0

2 (EP) address Data 1 0 0

3 N +3 The following

following instruction

10 0

88 - 8F MOV Ri, #d8 3 1 N +2 The following

instruction

10 0

2 Rn address Data 0 1 0

3 N +3 The following

following instruction

10 0

98 - 9F CMP Ri, #d8 3 1 N +2 The following

instruction

10 0

2 Rn address Data 1 0 0

3 N +3 The following

following instruction

10 0

82 MOV @A, T 2 1 N +2 The following

following instruction

10 0

2 (A) address Data 0 1 0

92 MOV A, @A 2 1 N +2 The following

following instruction

10 0

2 (A) address Data 1 0 0

83 MOVW @A, T 3 1 N +2 The following

following instruction

10 0

2 (A) address Data (H byte) 0 1 0

3 (A) +1 address Data (L byte) 0 1 0

Table B-1 Bus Operation List (7/11)

CODE MNEMONIC ~ Cycle Address bus Data bus RD WR RMW